III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

B-III-10-18 EPSON S1C33210 FUNCTION PART

Mobile Access Interface Interrupts

Overview

The mobile access interface module generates eight interrupt requests, mapped according to the communications

mode under program control to five interrupt request lines to the CPU core.

Interrupt Types

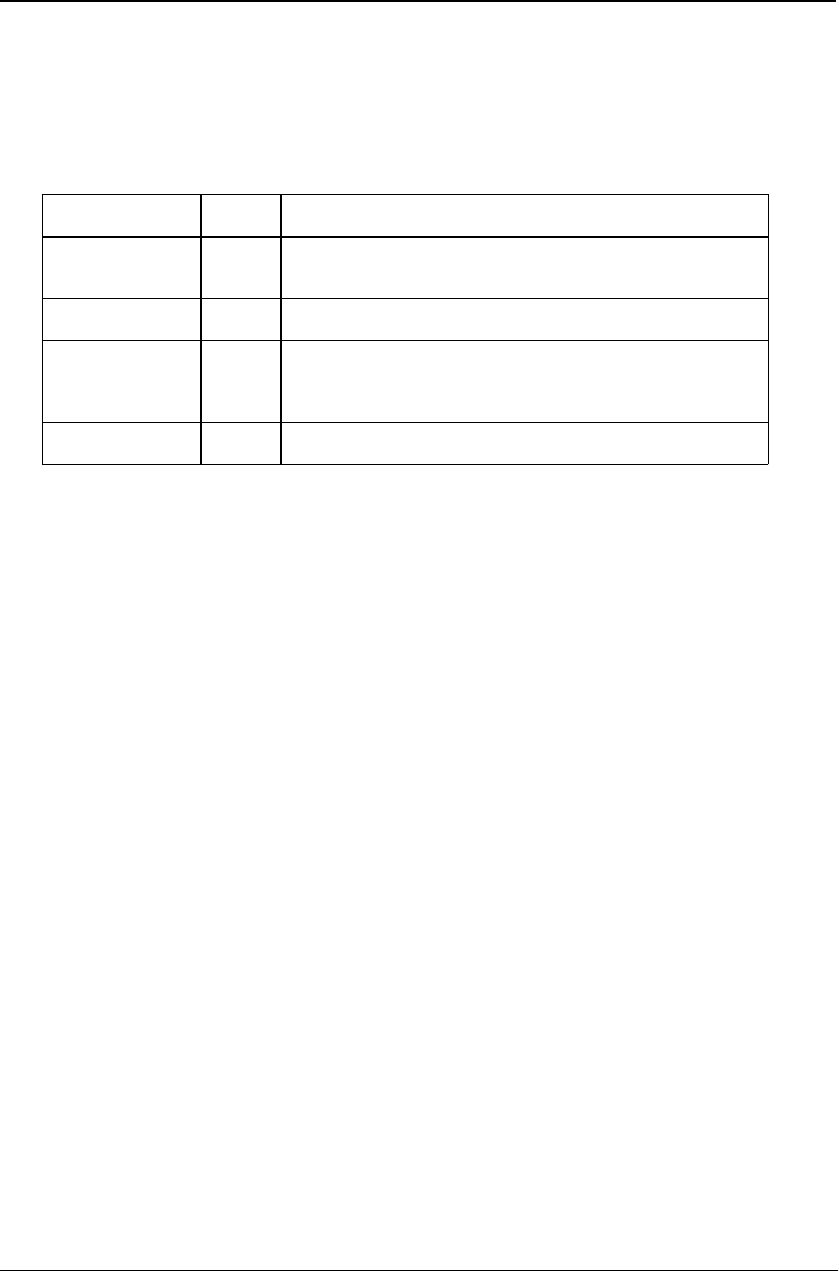

Table 10.8 lists the interrupt requests for each communications mode.

Table 10.8 Interrupt Types

Communications

mode

Symbol Interrupt Types

PDC

communications

mode

PDCINT PDC interrupt

PHS communications

mode

PRINT

PTINT

PHS receive interrupt

PHS transmit interrupt

HDLC

communications

mode

RXINT

TXINT

SPINT

ESINT

HDLC receive interrupt

HDLC transmit interrupt

HDLC Sp interrupt

HDLC E/S interrupt

All communications

modes

MSINT Modem status change interrupt

Note:The UART communications mode uses serial interface Ch. 3 transmit and receive interrupts.

(1) PDCINT = PDC interrupt

Interrupt source Falling edge in PDC frame signal input

Condition Every 20 ms, at falling edges in the PDC frame signal, regardless of the TXEN and RXEN

settings in the PDC command register

To clear Write "1" to the PDCINT bit (D0/0x0200100)

(2) PRINT = PHS receive interrupt

Interrupt source Receiving frame data from PHS device

Condition Receiving 640-bit PIAFS frame. Every 20 ms for 32 kbps operation, every 10 ms for 64 kbps

operation

To clear Write "1" to the RXINT bit in the PHS receive status register (D7/0x0200206)

(3) PTINT = PHS transmit interrupt

Interrupt source Completion of frame transmission to PHS device

Condition Transmission of 640-bit PIAFS frame. Every 20 ms for 32 kbps operation, every 10 ms for 64

kbps operation

To clear Write "1" to the TXINT bit in the PHS transmit status register (D7/0x0200202)

(4) RXINT = HDLC receive interrupt

Interrupt source The data in the receive queue or receive block satisfies the conditions below.

Condition 1. If the setting specifies Rx INT and Sp INT on first character received, when the hardware

receives the first byte

• after a reset (hardware or software) or

• after the software writes "1" to the Rx INT on next receive character command bit in

the HDLC receive control register (D0/0x0200314).

2. If the setting specifies Rx INT and Sp INT on queue threshold, when the number of

characters in the receive queue exceeds the threshold setting in the HDLC receive queue

interrupt threshold register (D[2:0]/0x0200310).

To clear Write "1" to the reset Tx INT bit