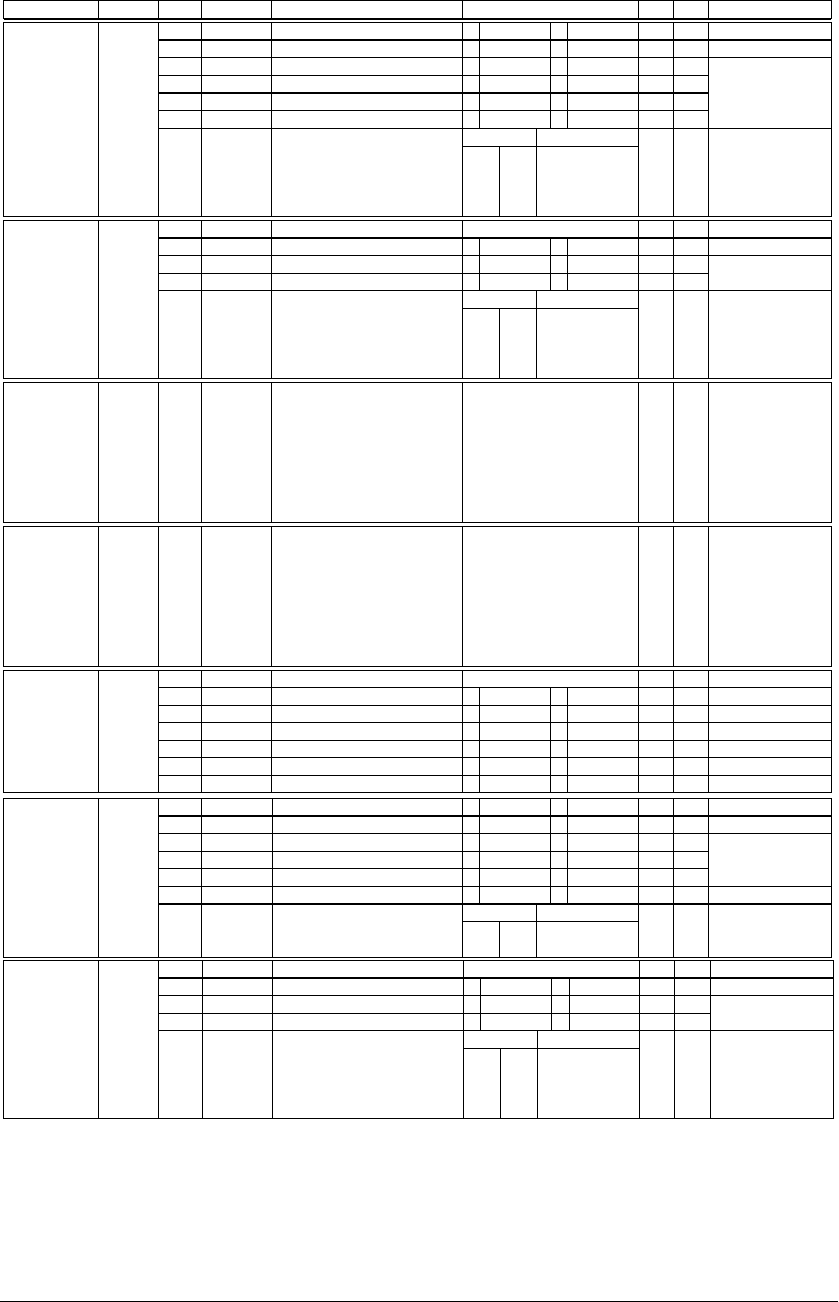

4 PERIPHERAL CIRCUITS

S1C33210 PRODUCT PART EPSON A-25

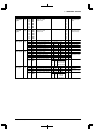

NameAddressRegister name Bit Function Setting Init. R/W Remarks

TXEN2

RXEN2

EPR2

PMD2

STPB2

SSCK2

SMD21

SMD20

D7

D6

D5

D4

D3

D2

D1

D0

Ch.2 transmit enable

Ch.2 receive enable

Ch.2 parity enable

Ch.2 parity mode selection

Ch.2 stop bit selection

Ch.2 input clock selection

Ch.2 transfer mode selection

1

1

0

0

1

0

1

0

SMD2[1:0] Transfer mode

8-bit asynchronous

7-bit asynchronous

Clock sync. Slave

Clock sync. Master

0

0

X

X

X

X

X

X

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Valid only in

asynchronous mode.

00401F3

(B)

Serial I/F Ch.2

control register

1 Enabled 0 Disabled

1 Enabled 0 Disabled

1 With parity 0 No parity

1 Odd 0 Even

1 2 bits 0 1 bit

1 #SCLK2 0

Internal clock

–

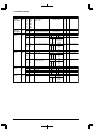

DIVMD2

IRTL2

IRRL2

IRMD21

IRMD20

D7–5

D4

D3

D2

D1

D0

reserved

Ch.2 async. clock division ratio

Ch.2 IrDA I/F output logic inversion

Ch.2 IrDA I/F input logic inversion

Ch.2 interface mode selection

1

1

0

0

1

0

1

0

IRMD2[1:0]

–

I/F mode

reserved

IrDA 1.0

reserved

General I/F

–

X

X

X

X

X

–

R/W

R/W

R/W

R/W

0 when being read.

Valid only in

asynchronous mode.

00401F4

(B)

1 1/8 0 1/16

1 Inverted 0 Direct

1 Inverted 0 Direct

Serial I/F Ch.2

IrDA register

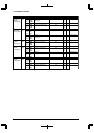

0x0 to 0xFF(0x7F)TXD37

TXD36

TXD35

TXD34

TXD33

TXD32

TXD31

TXD30

D7

D6

D5

D4

D3

D2

D1

D0

Serial I/F Ch.3 transmit data

TXD37(36) = MSB

TXD30 = LSB

X

X

X

X

X

X

X

X

R/W00401F5

(B)

Serial I/F Ch.3

transmit data

register

0x0 to 0xFF(0x7F)RXD37

RXD36

RXD35

RXD34

RXD33

RXD32

RXD31

RXD30

D7

D6

D5

D4

D3

D2

D1

D0

Serial I/F Ch.3 receive data

RXD37(36) = MSB

RXD30 = LSB

X

X

X

X

X

X

X

X

R00401F6

(B)

Serial I/F Ch.3

receive data

register

–

TEND3

FER3

PER3

OER3

TDBE3

RDBF3

D7–6

D5

D4

D3

D2

D1

D0

reserved

Ch.3 transmit-completion flag

Ch.3 flaming error flag

Ch.3 parity error flag

Ch.3 overrun error flag

Ch.3 transmit data buffer empty

Ch.3 receive data buffer full

–

0

0

0

0

1

0

–

R

R/W

R/W

R/W

R

R

0 when being read.

Reset by writing 0.

Reset by writing 0.

Reset by writing 0.

00401F7

(B)

–

1 Error 0 Normal

1

Transmitting

0 End

1 Error 0 Normal

1 Error 0 Normal

1 Empty 0 Buffer full

1 Buffer full 0 Empty

Serial I/F Ch.3

status register

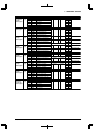

TXEN3

RXEN3

EPR3

PMD3

STPB3

SSCK3

SMD31

SMD30

D7

D6

D5

D4

D3

D2

D1

D0

Ch.3 transmit enable

Ch.3 receive enable

Ch.3 parity enable

Ch.3 parity mode selection

Ch.3 stop bit selection

Ch.3 input clock selection

Ch.3 transfer mode selection

1

1

1

0

SMD3[1:0] Transfer mode

8-bit asynchronous

7-bit asynchronous

0

0

X

X

X

X

X

X

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Always set to 0

Always set SMD31 to

1

00401F8

(B)

Serial I/F Ch.3

control register

1 Enabled 0 Disabled

1 Enabled 0 Disabled

1 With parity 0 No parity

1 Odd 0 Even

1 2 bits 0 1 bit

1 – 0

Internal clock

–

DIVMD3

IRTL3

IRRL3

IRMD31

IRMD30

D7–5

D4

D3

D2

D1

D0

reserved

Ch.3 async. clock division ratio

Ch.3 IrDA I/F output logic inversion

Ch.3 IrDA I/F input logic inversion

Ch.3 interface mode selection

1

1

0

0

1

0

1

0

IRMD3[1:0]

–

I/F mode

reserved

IrDA 1.0

reserved

General I/F

–

X

X

X

X

X

–

R/W

R/W

R/W

R/W

0 when being read.00401F9

(B)

1 1/8 0 1/16

1 Inverted 0 Direct

1 Inverted 0 Direct

Serial I/F Ch.3

IrDA register