III PERIPHERAL BLOCK: PRESCALER

B-III-2-2 EPSON S1C33210 FUNCTION PART

Selecting Division Ratio and Output Control for Prescaler

The prescaler has registers for selecting the division ratio and clock output control separately for each peripheral

circuit described above, allowing each peripheral circuit to be controlled.

The prescaler's division ratio can be selected from among eight ratios set for each peripheral circuit through the use of

the division ratio selection bits. The divided clock is output to the corresponding peripheral circuit by writing "1" to

the clock control bit.

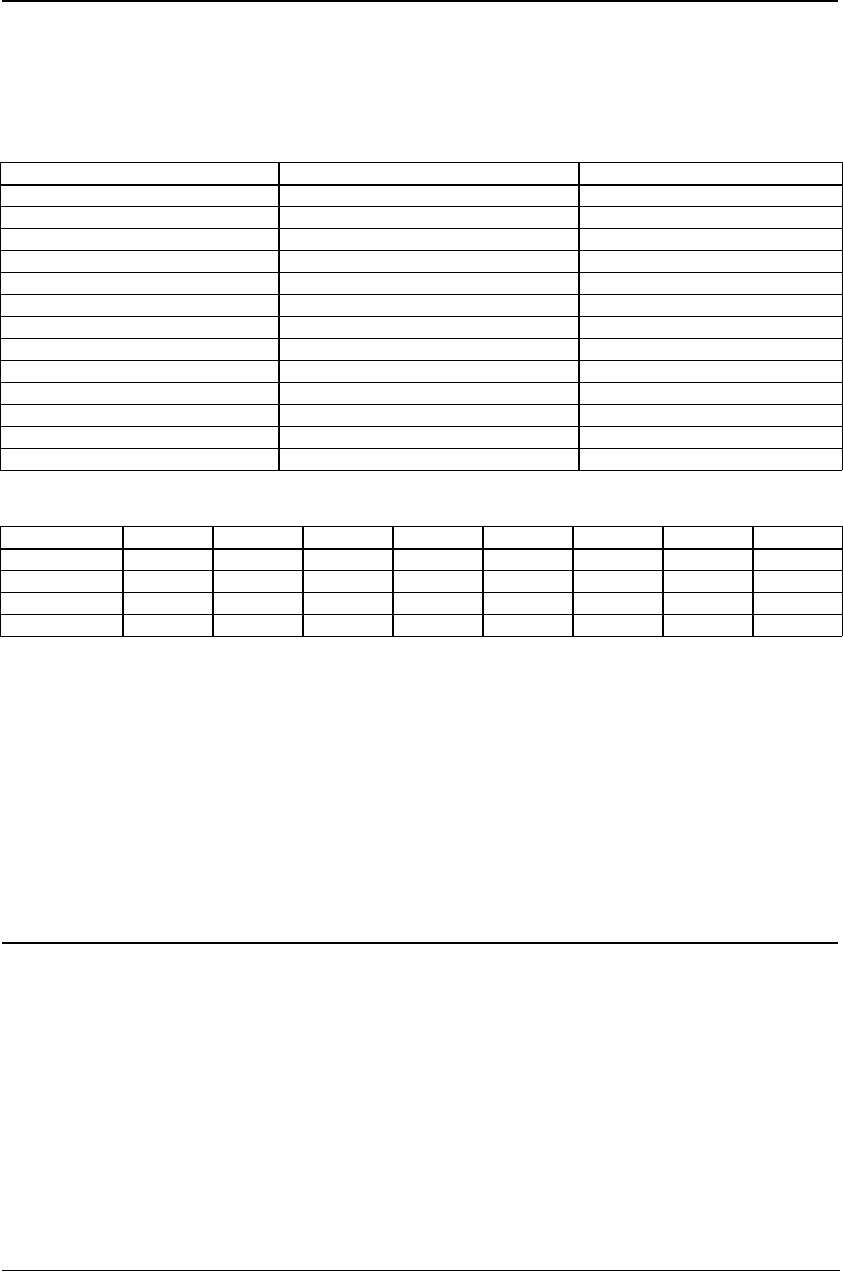

Table 2.1 Control Bits of the Clock Control Registers

Peripheral circuit Division ratio selection bit Clock control bit

16-bit programmable timer 0 P16TS0[2:0] (D[2:0]/0x40147)∗1 P16TON0 (D3/0x40147)

16-bit programmable timer 1 P16TS1[2:0] (D[2:0]/0x40148)∗1 P16TON1 (D3/0x40148)

16-bit programmable timer 2 P16TS2[2:0] (D[2:0]/0x40149)∗1 P16TON2 (D3/0x40149)

16-bit programmable timer 3 P16TS3[2:0] (D[2:0]/0x4014A)∗1 P16TON3 (D3/0x4014A)

16-bit programmable timer 4 P16TS4[2:0] (D[2:0]/0x4014B)∗1 P16TON4 (D3/0x4014B)

16-bit programmable timer 5 P16TS5[2:0] (D[2:0]/0x4014C)∗1 P16TON5 (D3/0x4014C)

8-bit programmable timer 0 P8TS0[2:0] (D[2:0]/0x4014D)∗2 P8TON0 (D3/0x4014D)

8-bit programmable timer 1 P8TS1[2:0] (D[6:4]/0x4014D)∗3 P8TON1 (D7/0x4014D)

8-bit programmable timer 2 P8TS2[2:0] (D[2:0]/0x4014E)∗4 P8TON2 (D3/0x4014E)

8-bit programmable timer 3 P8TS3[2:0] (D[6:4]/0x4014E)∗2 P8TON3 (D7/0x4014E)

8-bit programmable timer 4 P8TS4[2:0] (D[2:0]/0x40145)∗4 P8TON4 (D3/0x40145)

8-bit programmable timer 5 P8TS5[2:0] (D[6:4]/0x40145)∗2 P8TON5 (D7/0x40145)

A/D converter PSAD[2:0] (D[2:0]/0x4014F)∗2 PSONAD (D3/0x4014F)

∗1 to ∗4: See Table 2.2.

Table 2.2 Division Ratio

Bit setting 76543210

∗1 θ/4096 θ/1024 θ/256 θ/64 θ/16 θ/4 θ/2 θ/1

∗2 θ/256 θ/128 θ/64 θ/32 θ/16 θ/8 θ/4 θ/2

∗3 θ/4096 θ/2048 θ/1024 θ/512 θ/256 θ/128 θ/64 θ/32

∗4 θ/4096 θ/2048 θ/64 θ/32 θ/16 θ/8 θ/4 θ/2

(θ = Source clock selected by PSCDT0)

Current consumption can be reduced by turning off the clock output to the peripheral circuits that are unused among

those listed above.

Note: In the following cases, the prescaler output clock may contain a hazard:

• If, when a clock is output, its division ratio is changed

• When the clock output is switched between on and off

• When the oscillation circuit is turned off or the CPU operating clock is switched over

Before performing these operations, make sure the 16-bit and 8-bit programmable timers and the

A/D converter are turned off.

Source Clock Output to 8-Bit Programmable Timer

In addition to the divided clock, the prescaler can output the source clock directly to the 8-bit programmable timer.

This function can be selected for each 8-bit timer using P8TPCKx bit.

8-bit timer 0: P8TPCK0 (D0) / 8-bit timer clock select register (0x40146)

8-bit timer 1: P8TPCK1 (D1) / 8-bit timer clock select register (0x40146)

8-bit timer 2: P8TPCK2 (D2) / 8-bit timer clock select register (0x40146)

8-bit timer 3: P8TPCK3 (D3) / 8-bit timer clock select register (0x40146)

8-bit timer 4: P8TPCK4 (D0) / 8-bit timer 4/5 clock select register (0x40140)

8-bit timer 5: P8TPCK5 (D1) / 8-bit timer 4/5 clock select register (0x40140)

When P8TPCKx is set to "1", the prescaler input clock (θ/1) is selected for the 8-bit timer x operating clock.

The clock output is controlled by the P8TONx bit even if P8TPCKx is set to "1".

When P8TPCKx is "0", the divided clock that is selected by P8TSx[2:0] will be output to the 8-bit timer x.

At initial reset, P8TPCKx is set to "0" and P8TSx[2:0] becomes effective.