II CORE BLOCK: CLG (Clock Generator)

B-II-6-4 EPSON S1C33210 FUNCTION PART

Setting and Switching Over the CPU Operating Clock

Setting the CPU operating clock frequency

When operating the CPU with the high-speed (OSC3) clock, the operating frequency can be switched over in

four steps. Use CLKDT[1:0] (D[7:6]) / Power control register (0x40180) for this switchover.

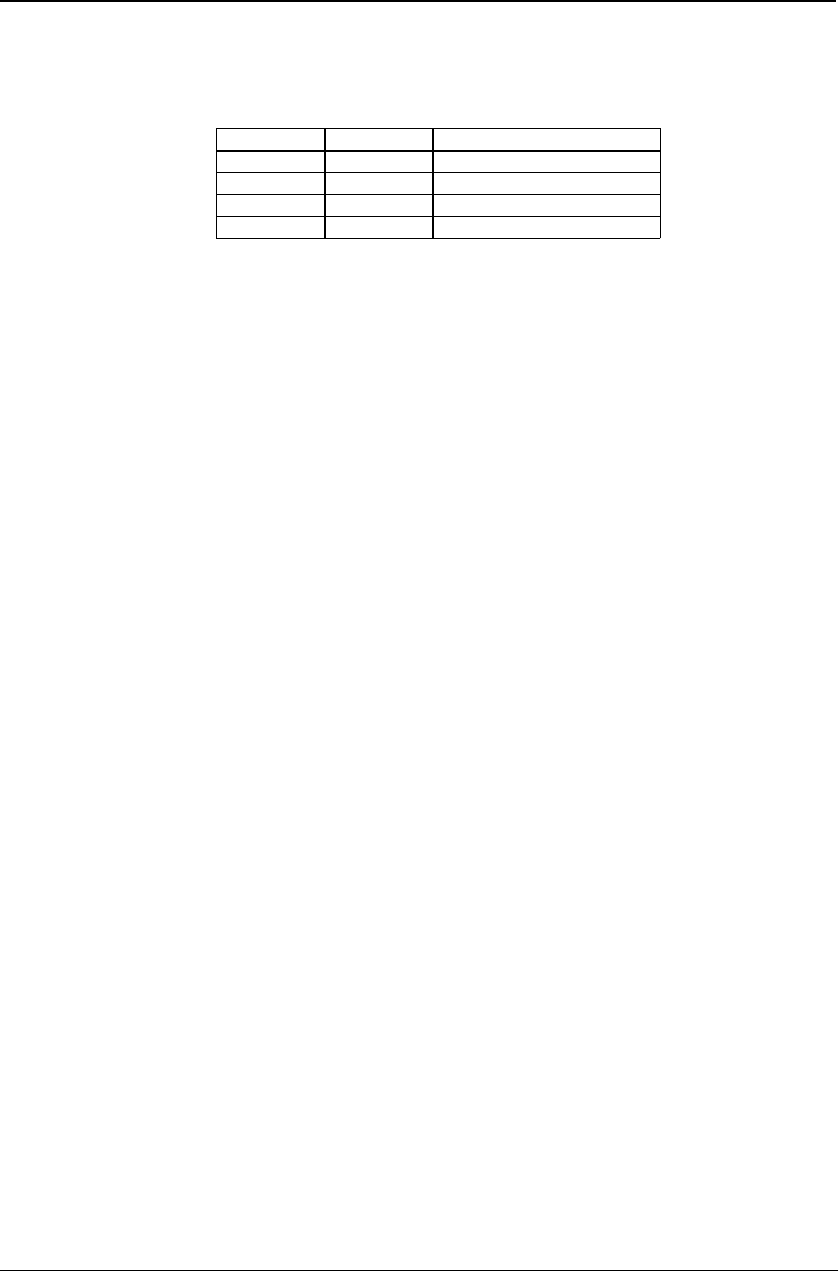

Table 6.3 Setting of CPU Operating Clock

CLKDT1 CLKDT0 Division ratio

1 1 fout/8

1 0 fout/4

0 1 fout/2

0 0 fout/1

fout: PLL output

The clock thus set becomes the system clock, which is used as the CPU operating clock and the bus clock.

At initial reset, the division ratio is set to fout/1, so the CPU is operated directly by the PLL output clock.

Since the device's current consumption can be decreased by reducing the CPU operating speed, switch over the

operating frequency as necessary.

This setting is effective only for the high-speed (OSC3) clock, and has no effect when the low-speed (OSC1)

clock is used as the system clock.

Note: Writing to CLKDT[1:0] is effective only when the power-control register protection flag is set to

"0b10010110".

Switching over the CPU operating clock

Note: The CPU operating clock can be switched from OSC3 to OSC1 only when the low-speed (OSC1)

oscillation circuit in the peripheral block is used.

After an initial reset, the CPU starts operating using the OSC3 clock. All internal peripheral circuits also

operate.

If operation of the peripheral circuits (programmable timers, serial interface, A/D converter, ports, and other

circuits) is not required or if their required processing can be performed at a lower speed, and if the CPU can also

be operated at a lower speed, the CPU operating clock can be switched to the OSC1 clock, thereby reducing

current consumption. Use CLKCHG (D2) / Power control register (0x40180) to switch this operating clock.

Procedure for switching over from the OSC3 clock to the OSC1 clock

1. Turn on the low-speed (OSC1) oscillation circuit (by writing "1" to SOSC1).

2. Wait until the OSC1 oscillation stabilizes (three seconds or more).

3. Change the CPU operating clock (by writing "0" to CLKCHG).

4. Turn off the high-speed (OSC3) oscillation circuit (by writing "0" to SOSC3).

∗ Steps 1 and 2 are required only when the low-speed (OSC1) oscillation circuit is inactive.

Notes: • Use separate instructions to switch from OSC3 to OSC1 and turn the OSC3 oscillation off. If

these operations are processed simultaneously using one instruction, the CPU may operate

erratically.

• To prevent incorrect operation of peripheral circuits such as the programmable timers, A/D

converter, and serial interface, before stopping the OSC3 oscillator, either stop these circuits or

set the prescaler clock to be OSC1. Note that to prevent incorrect operation, the prescaler clock

must be set before the CPU clock is changed.

Procedure for switching over from the OSC1 clock to the OSC3 clock

1. Turn on the high-speed (OSC3) oscillation circuit (by writing "1" to SOSC3).

2. Wait until the OSC3 oscillation stabilizes (10 ms or more for a 3.3-V crystal resonator).

3. Switch over the CPU operating clock (by writing "1" to CLKCHG).

Note: The operating clock switchover by CLKCHG is effective only when both oscillation circuits are on

and the power-control register protection flag is set to "0b10010110".