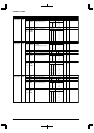

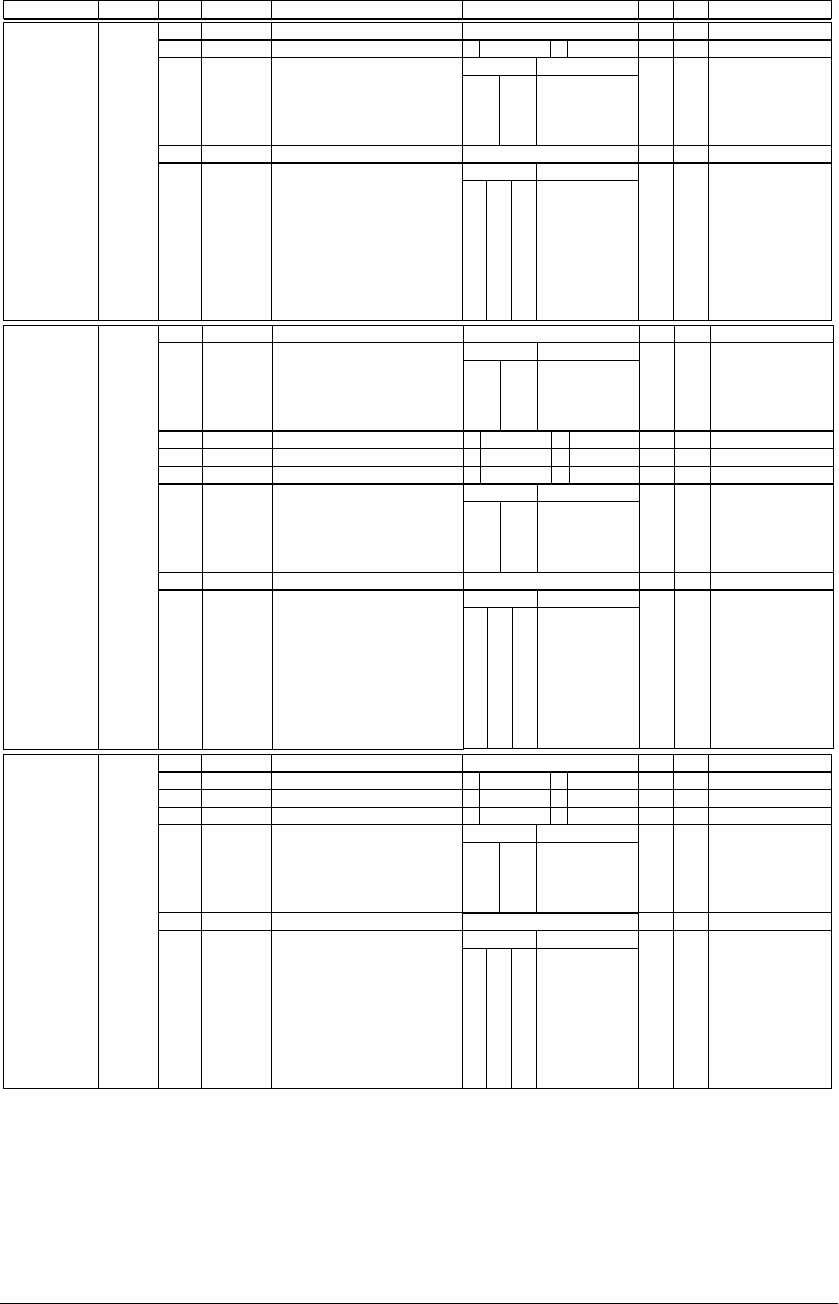

APPENDIX: I/O MAP

B-APPENDIX-24 EPSON S1C33210 FUNCTION PART

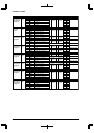

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

A12SZ

A12DF1

A12DF0

–

A12WT2

A12WT1

A12WT0

DF–7

D6

D5

D4

D3

D2

D1

D0

reserved

Areas 12–11 device size selection

Areas 12–11

output disable delay time

reserved

Areas 12–11 wait control

–

–

1 8 bits 0 16 bits

–

0

1

1

–

1

1

1

–

R/W

R/W

–

R/W

0 when being read.

0 when being read.

0048124

(HW)

Areas 12–11

set-up register

1

1

0

0

1

0

1

0

A18DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A18WT[2:0] Wait cycles

7

6

5

4

3

2

1

0

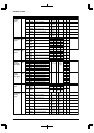

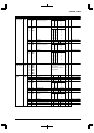

–

A10BW1

A10BW0

A10DRA

A9DRA

A10SZ

A10DF1

A10DF0

–

A10WT2

A10WT1

A10WT0

DF-B

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Areas 10–9

burst ROM

burst read cycle wait control

Area 10 burst ROM selection

Area 9 burst ROM selection

Areas 10–9 device size selection

Areas 10–9

output disable delay time

reserved

Areas 10–9 wait control

––

–

1 Used 0 Not used

1 Used 0 Not used

1 8 bits 0 16 bits

–

0

0

0

0

0

1

1

–

1

1

1

–

R/W

R/W

R/W

R/W

R/W

–

R/W

0 when being read.

0 when being read.

0048126

(HW)

1

1

0

0

1

0

1

0

A10BW[1:0] Wait cycles

3

2

1

0

1

1

0

0

1

0

1

0

A10DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A10WT[2:0] Wait cycles

7

6

5

4

3

2

1

0

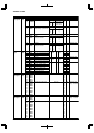

Areas 10–9

set-up register

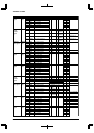

–

A8DRA

A7DRA

A8SZ

A8DF1

A8DF0

–

A8WT2

A8WT1

A8WT0

DF–9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

Area 8 DRAM selection

Area 7 DRAM selection

Areas 8–7 device size selection

Areas 8–7

output disable delay time

reserved

Areas 8–7 wait control

–

–

1 Used 0 Not used

1 Used 0 Not used

1 8 bits 0 16 bits

–

0

0

0

1

1

–

1

1

1

–

R/W

R/W

R/W

R/W

–

R/W

0 when being read.

0 when being read.

0048128

(HW)

Areas 8–7

set-up register

1

1

0

0

1

0

1

0

A8DF[1:0] Number of cycles

3.5

2.5

1.5

0.5

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

A8WT[2:0] Wait cycles

7

6

5

4

3

2

1

0