III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

S1C33210 FUNCTION PART EPSON B-III-10-39

RXD[7:0]: HDLC receive data (D[7:0]) / HDLC receive data register (0x0200316)

This read-only register is for reading bytes from the receive queue, updating both the queue and the status registers.

(For further details on the latter, see the descriptions of the status registers.)

The HDLC interface receives the LSB (bit 0) first.

Note that the software must read the Rx Statuses cause of Sp INT register before the receive data register because

reading the latter updates the former.

If the queue is empty––after a reset, for example--reads return indeterminate data until the next byte enters the queue

from the receive shift register.

This register is read only. Writes are ignored.

RESID: HDLC residue detected(D2) / HDLC receive status register (0x0200330)

RCA: HDLC receive character available (RCA, D1) / HDLC receive status register (0x0200330)

CRCER: HDLC CRC error detected (D0) / HDLC receive status register (0x0200330)

These bits give the status of conditions that do not trigger interrupt requests.

A "1" in RESID indicates that the current frame does not end on a byte boundary. The residue code bits specify the

number of valid bits in the last byte. This bit remains valid from immediately after detection of the end of frame

(EOF) up to the start of the next frame.

A "1" in RCA indicates that the receive queue contains data available for reading. If the receive queue interrupt

threshold setting is zero, there is an Rx INT interrupt when this bit goes to "1." Otherwise, the two timings do not

necessarily match.

A "1" in CRCER indicates failure of the CRC check. This bit is only valid when EOF is "1." It returns to "0" at the

start of the next frame. The error reset command does not reset this bit. Changes in this bit do not produce interrupt

requests.

RCODE[7:0]: HDLC residue code (D[7:0]) / HDLC residue code register (0x0200332)

These bits specify the number of valid bits in the last byte for a frame that does not end on a byte boundary.

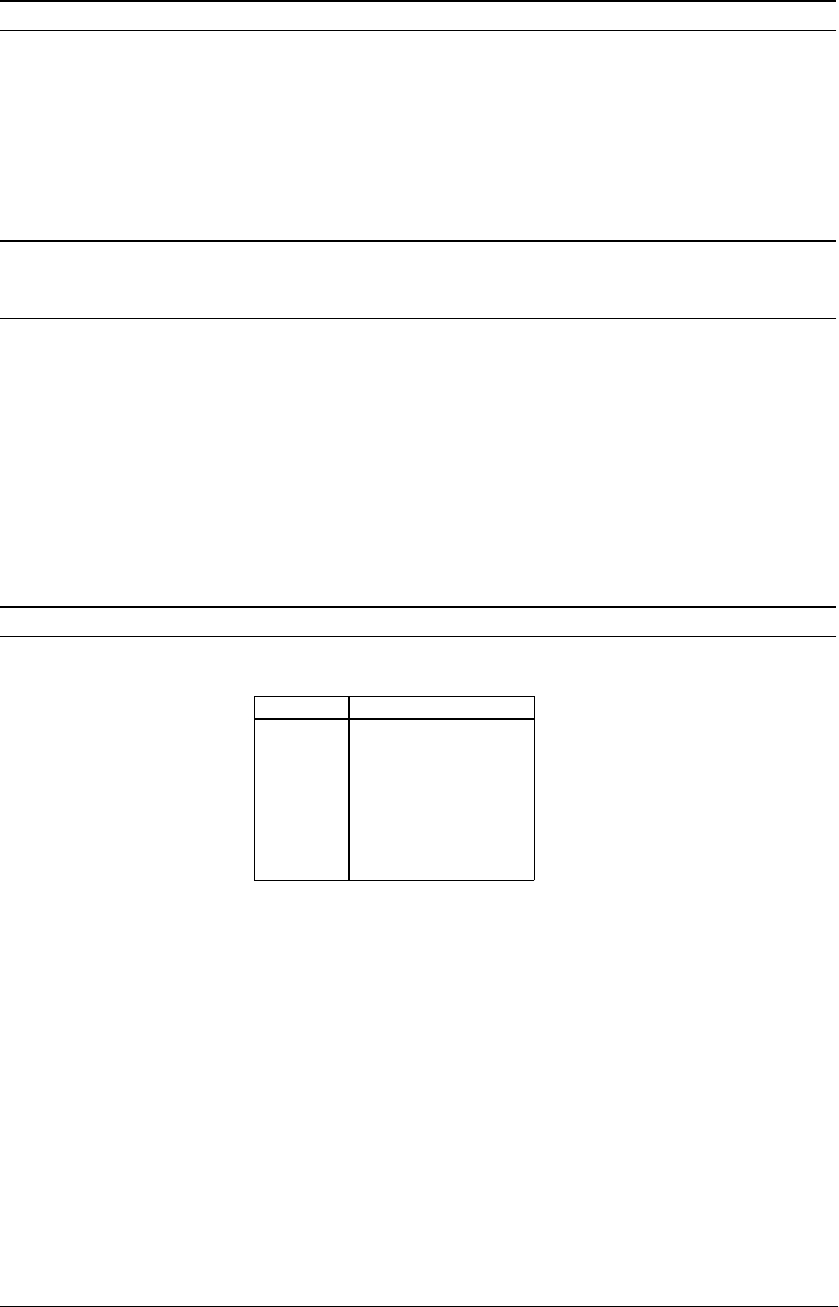

Table 10.21 Residue Bits

Number Valid Bit Positions

7

6

5

4

3

2

1

MSB LSB

1 1 1 1 1 1 1 0

1 1 1 1 1 1 0 0

1 1 1 1 1 0 0 0

1 1 1 1 0 0 0 0

1 1 1 0 0 0 0 0

1 1 0 0 0 0 0 0

1 0 0 0 0 0 0 0

("1" indicates a valid bit)

These bits are only valid when the RESID bit in the HDLC receive status register (D2/0x02000330) is "1." They

have no meaning when RESID is "0."

The software must read these bits by the end of the next frame because the hardware updates them at the end of each

frame regardless of the RESID contents.