IV ANALOG BLOCK: A/D CONVERTER

S1C33210 FUNCTION PART EPSON B-IV-2-7

A/D Converter Interrupt and DMA

Upon completion of A/D conversion in each channel, the A/D converter generates an interrupt and invokes the DMA

if necessary.

Control registers of the interrupt controller

The following shows the interrupt control registers available for the A/D converter:

Interrupt factor flag: FADE (D0) / Port input 4–7, clock timer, A/D interrupt factor flag register (0x40287)

Interrupt enable: EADE (D0) / Port input 4–7, clock timer, A/D interrupt enable register (0x40277)

Interrupt level: PAD[2:0] (D[6:4]) / Serial I/F Ch.1, A/D interrupt priority register (0x4026A)

The A/D converter sets the interrupt factor flag to "1" when A/D conversion in one channel is completed, and

the conversion results are stored in the ADD register. At this time, if the interrupt enable register bit has been

set to "1", an interrupt request is generated.

Interrupts can be disabled by leaving the interrupt enable register bit set to "0". The interrupt factor flag is set

to "1" upon completion of A/D conversion in each channel, regardless of the setting of the interrupt enable

register (even when it is set to "0").

The interrupt priority register sets the priority level (0 to 7) of an interrupt. An interrupt request to the CPU is

accepted no other interrupt request of a higher priority has been generated.

In addition, it is only when the PSR's IE bit = "1" (interrupts enabled) and the set value of the IL is smaller than

the A/D-converter interrupt level set by the interrupt priority register, that the A/D converter's interrupt request

is actually accepted by the CPU.

For details on these interrupt control registers, as well as the device operation when an interrupt has occurred,

refer to "ITC (Interrupt Controller)".

Intelligent DMA

The A/D converter can invoke the intelligent DMA (IDMA) through the use of its interrupt factor. This allows

the conversion results to be transferred to a specified memory location with no need to execute an interrupt

processing routine.

The IDMA channel number assigned to the A/D converter is 0x1B.

Before IDMA can be invoked, the IDMA request and IDMA enable bits must be set to "1". Transfer conditions

on the IDMA side must also be set in advance.

IDMA request: RADE (D2)/ Serial I/F Ch.1, A/D, Port input 4–7 IDMA request register (0x40293)

IDMA enable: DEADE (D2)/ Serial I/F Ch.1, A/D, Port input 4–7 IDMA enable register (0x40297)

If an interrupt factor occurs when the IDMA request and IDMA enable bits are set to "1", IDMA is invoked.

No interrupt request is generated at that point. An interrupt request is generated upon completion of the DMA

transfer. Otherwise, the bit can be set so as not to generate an interrupt, with only a DMA transfer performed.

For details on DMA transfers and how to control interrupts upon completion of a DMA transfer, refer to

"IDMA (Intelligent DMA)".

High-speed DMA

The A/D interrupt factor can also invoke high-speed DMA (HSDMA).

The following shows the HSDMA channel number and trigger set-up bit:

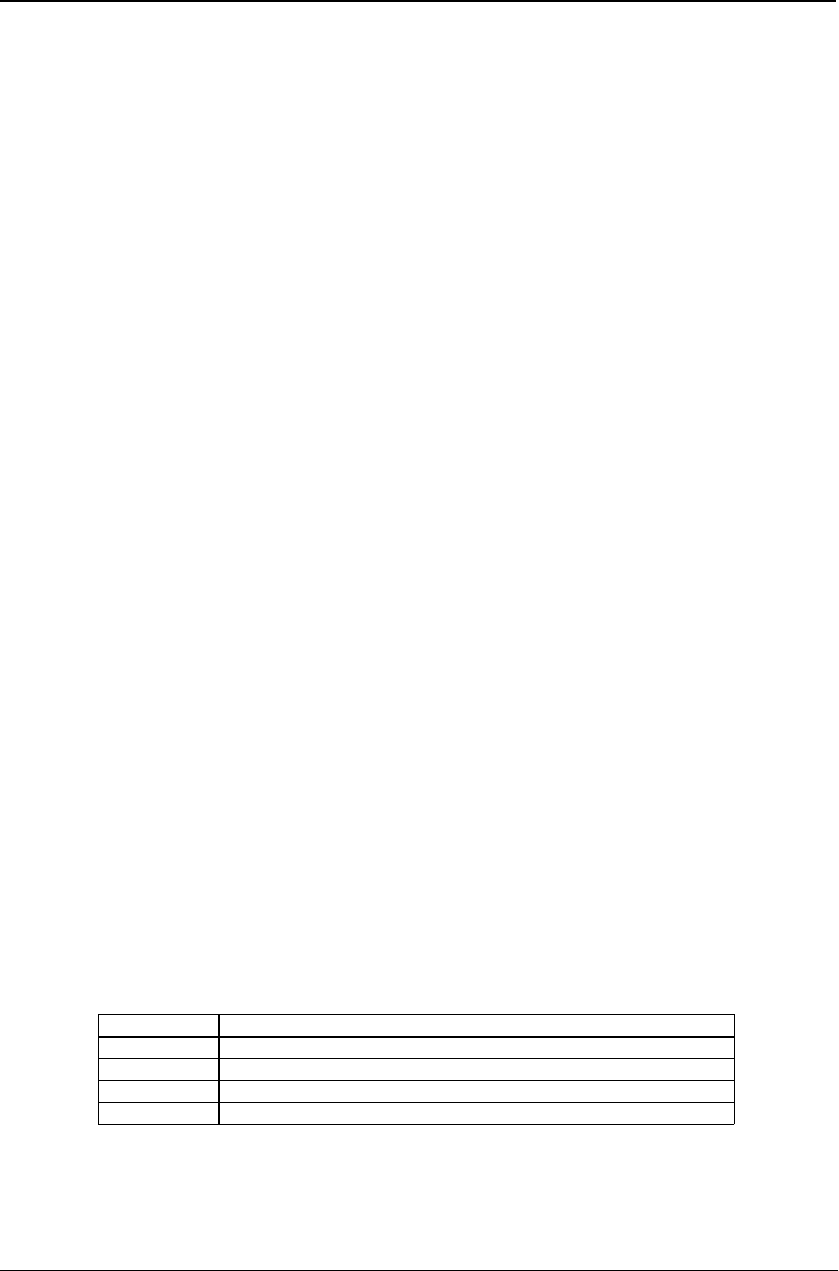

Table 2.5 HSDMA Trigger Set-up Bits

HSDMA channel Trigger set-up bits

0 HSD0S[3:0] (D[3:0]) / HSDMA Ch.0/1 trigger set-up register (0x40298)

1 HSD1S[3:0] (D[7:4]) / HSDMA Ch.0/1 trigger set-up register (0x40298)

2 HSD2S[3:0] (D[3:0]) / HSDMA Ch.2/3 trigger set-up register (0x40299)

3 HSD3S[3:0] (D[7:4]) / HSDMA Ch.2/3 trigger set-up register (0x40299)

For HSDMA to be invoked, the trigger set-up bits should be set to "1100" in advance. Transfer conditions, etc.

must also be set on the HSDMA side.

If the A/D interrupt factor is selected as the HSDMA trigger, the HSDMA channel is invoked through

generation of the interrupt factor.

For details on HSDMA transfer, refer to "HSDMA (High-Speed DMA)".