III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

S1C33210 FUNCTION PART EPSON B-III-10-25

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

RCODE7

RCODE6

RCODE5

RCODE4

RCODE3

RCODE2

RCODE1

RCODE0

D15–8

D7

D6

D5

D4

D3

D2

D1

D0

–

HDLC residue code

–

11111110

11111100

11111000

11110000

11100000

11000000

10000000

RCODE[7:0] Effective bits

7

6

5

4

3

2

1

–

X

X

X

X

X

X

X

X

–

R

0 when being read.

Only valid when

RESID = 1

0200332

(HW)

HDLC residue

code register

–

TXUE

TXBRDY

–

TXUDR

D15–8

D7

D6

D5–1

D0

–

HDLC Tx underrun/EOM

HDLC transmit buffer ready

–

HDLC Tx underrun

–

–

–

X

X

–

X

–

R

R

–

R

0 when being read.

0 when being read.

0200334

(HW)

HDLC transmit

status register

1 not Full 0 Full

1 Yes 0 No

1 Underrun 0

No underrun

–

ESINT

SPINT

RXINT

TXINT

–

D15–8

D7

D6

D5

D4

D3–0

–

HDLC E/S INT monitored

HDLC Sp INT monitored

HDLC Rx INT monitored

HDLC Tx INT monitored

–

–

–

–

X

X

X

X

–

–

R

R

R

R

–

0 when being read.

0 when being read.

0200336

(HW)

1

Request pending

0

No interrupts

1

Request pending

0

No interrupts

1

Request pending

0

No interrupts

1

Request pending

0

No interrupts

HDLC monitor

register

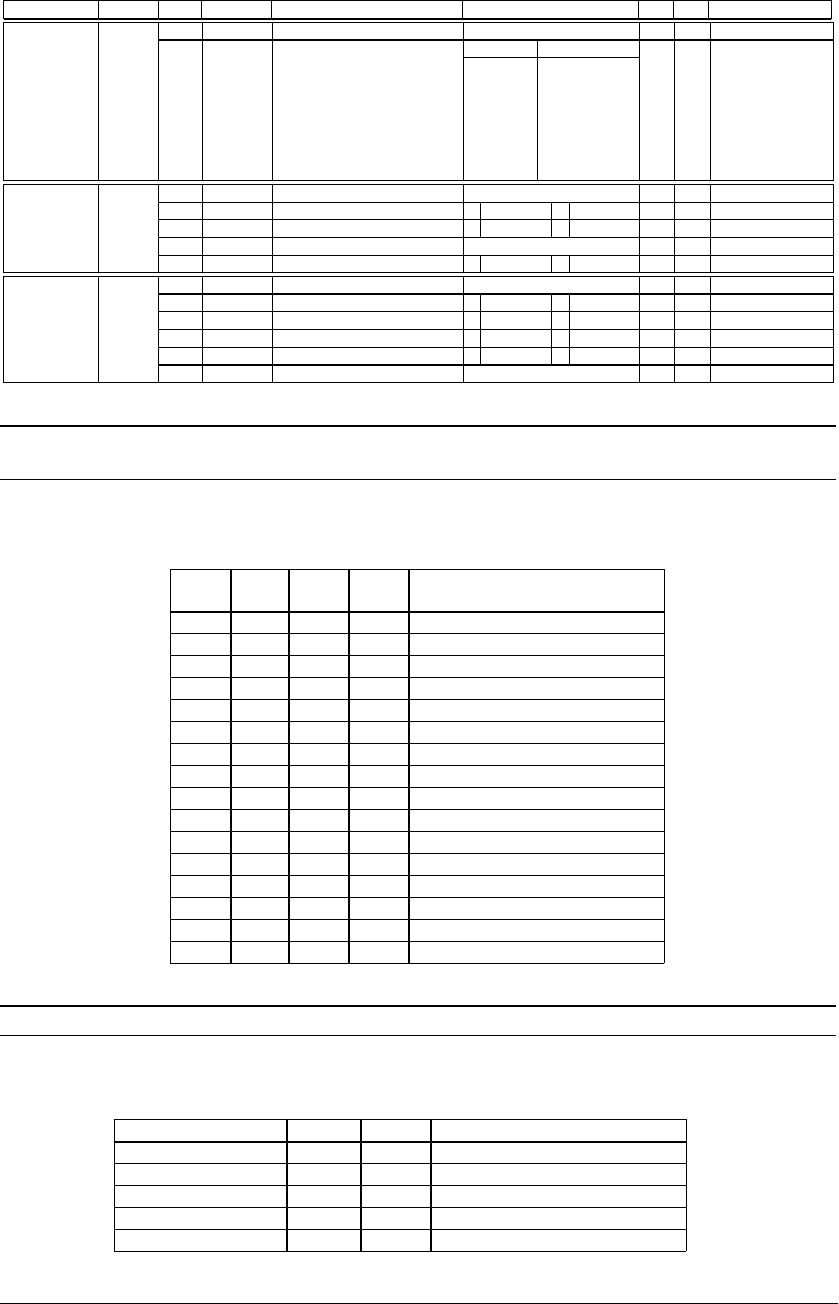

CKD3–CKD0: Clock frequency divider (D[3:0]) / Communications block clock frequency divider register

(0x0200004)

These bits specify the divisor for deriving the communications block clock (SCK) signal from the PERICLK clock

signal.

Table 10.12 Communications Block Clock (SCK) Frequency

CKD3 CKD2 CKD1 CKD0 SCK Clock Frequency Divider

Settings

1111 fout/16

1110 fout/15

1101 fout/14

1100 fout/13

1011 fout/12

1010 fout/11

1001 fout/10

1000 fout/9

0111 fout/8

0110 fout/7

0101 fout/6

0100 fout/5

0011 fout/4

0010 fout/3

0001 fout/2

0000 fout/2

fout = PERICLK output frequency

MCRS1–MCRS0: Communications macro select (D[1:0]) / Communications macro select register (0x200000)

These bits, together with the MSEL external pin input, specify the communications mode and thus configures the

I/O pin the I/O signals to match the target mobile device.

Table 10.13 Communications Modes

U_OUTCNT(MSEL) MCRS1 MCRS0 Communications Mode

1 1 1 PHS communications

1 1 0 PDC communications

1 0 1 HDLC communications

1 0 0 UART communications

0 X X Serial IF Ch. 3 (asynchronous)