III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

B-III-10-14 EPSON S1C33210 FUNCTION PART

HDLC Communications Mode

Overview

The HDLC communications mode processes HDLC frames for data transfers with PDC devices supporting packets.

For a transmit operation, this mode transmits an opening flag pattern, the data from a built-in 8-bit, 4-stage queue

(LSB first), a CRC, and a closing flag pattern. Outside flag patterns, the hardware automatically inserts a "0" after

six "1" bits in a row. The hardware can also force transmission of an abort pattern (eight "1" bits).

For a receive operation, this mode waits for an opening flag pattern, saves the data following it into a built-in 8-bit,

8-stage queue, checks the CRC, and reports the results in a register. In the process, it automatically deletes any extra

zero bits inserted. This mode also detects abort signals, idle states, and short frames.

This mode sends four types of interrupt requests to the CPU: HDLC transmit interrupts, HDLC receive interrupts,

HDLC extra source status (HDLC_ES) interrupts, and HDLC special condition (HDLC_SP) interrupts.

For communications macro select (MCRS) register (D[1:0]/0x200000) settings other than 00–that is, HDLC, PDC,

and PHS communications modes–the MOPORT3 and MOPORT2 bits in the communications block output port data

register (D[3:0]/0x020000A) drive the RTS and DTR pins using negative logic.

The MIPORT[1:0] bits in the communications block input port data register (D[1:0]/0x020000C) track the input

levels for the DSR and RI pins.

Frame Format

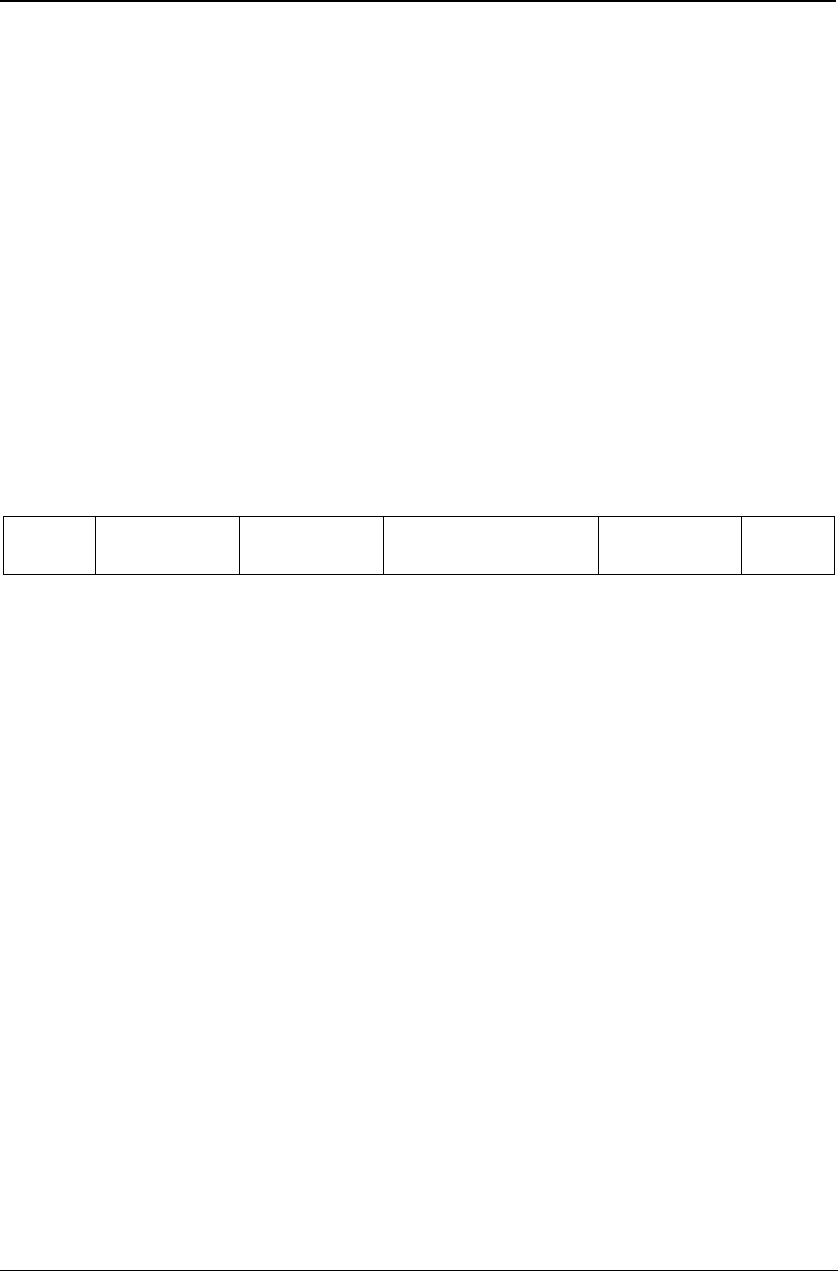

Figure 10.13 summarizes the HDLC serial data signal format for HDLC communications.

The receive circuit supports sharing between the closing flag pattern and the next opening flag pattern. It also

supports "0" sharing for sequential flag patterns.

Flag

'01111110'

Address Field

8 bits

Control Field

8 bits

Data field

(arbitrary length)

FCS (CRC)

16 bits

Flag

'01111110'

Figure 10.13 HDLC Communications Basic Frame Format

FCS (CRC) Checking

HDLC communications uses the following FCS (CRC) polynomial for validating frame data integrity.

CRC-CCITT: G(χ) = χ

16

+ χ

12

+ χ

5

+ 1

The FCS (CRC) calculation applies to everything from the address through data fields.

Output Port Control

For communications macro select (MCRS) register (D[1:0]/0x200000) settings other than 00--that is, HDLC,

PDC, and PHS communications modes--the MOPORT3 and MOPORT2 bits in the communications block

output port data register (D[3:0]/0x020000A) drive the RTS and DTR pins using negative logic.

Input Port Control

Input Port Monitoring The MIPORT[1:0] bits in the communications block input port data register

(D[1:0]/0x020000C) track the input levels for the DSR and RI pins. Note that the block does not store these

values internally.

In this mode as in others, setting the GOUTE bit in the communications block input port data register

(D7/0x020000C) to "1" connects the RI input to the GOUT output pin.

Note: Bits in the communications block modem status register (0x020002A) also track the input levels for

the DSR and RI pins as well as transitions for triggering interrupt requests with changes in pin

states.