III PERIPHERAL BLOCK: MONITORED MOBILE ACCESS INTERFACES

B-III-10-28 EPSON S1C33210 FUNCTION PART

SDRI, SURI, SDCTS, SUCTS, SDDCD, SUDCD, SDDSR, SUDSR: Modem status (D[7:0]) / Communications block

modem status register (0x020002A)

For reads, these bit pairs indicate changes in the input level for the corresponding status bit.

SDRI; Read "1": RI status has changed from "1" to "0"

Read "0": RI status hasn't changed from "1" to "0"

SURI; Read "1": RI status has changed from "0" to "1"

Read "0": RI status hasn't changed from "0" to "1"

Writing "1" to a bit resets it to "0." Writes of "0" are ignored.

SDRI; Write "1": SDRI status is reset

Write "0": Invalid

SURI; Write "1": SURI status is reset

Write "0": Invalid

There is a modem status change interrupt request when a bit goes to "1" if the corresponding bit in the

communications block modem status interrupt enable register enables such interrupts.

EDRI: Enable communications block SDRI modem status change interrupt (D7) / Communications block

modem status interrupt enable register (0x020002C)

EURI: Enable communications block SURI modem status change interrupt (D6) / Communications block

modem status interrupt enable register (0x020002C)

EDCTS: Enable communications block SDCTS modem status change interrupt (D5) / Communications

block modem status interrupt enable register (0x020002C)

EUCTS: Enable communications block SUCTS modem status change interrupt (D4) / Communications

block modem status interrupt enable register (0x020002C)

EDDCD:Enable communications block SDDCD modem status change interrupt (D3) / Communications

block modem status interrupt enable register (0x020002C)

EUDCD:Enable communications block SUDCD modem status change interrupt (D2) / Communications

block modem status interrupt enable register (0x020002C)

EDDSR:Enable communications block SDDSR modem status change interrupt (D1) / Communications

block modem status interrupt enable register (0x020002C)

EUDSR:Enable communications block SUDSR modem status change interrupt (D0) / Communications

block modem status interrupt enable register (0x020002C)

Enable or disable interrupt generation by the factors corresponding Communications block modem status interrupt

enable register (SDRI, SURI, SDCTS, SUCTS, SDDCD, SUDCD, SDDSR, or SUDSR).

Write "1": Interrupt enabled

Write "0": Interrupt disabled

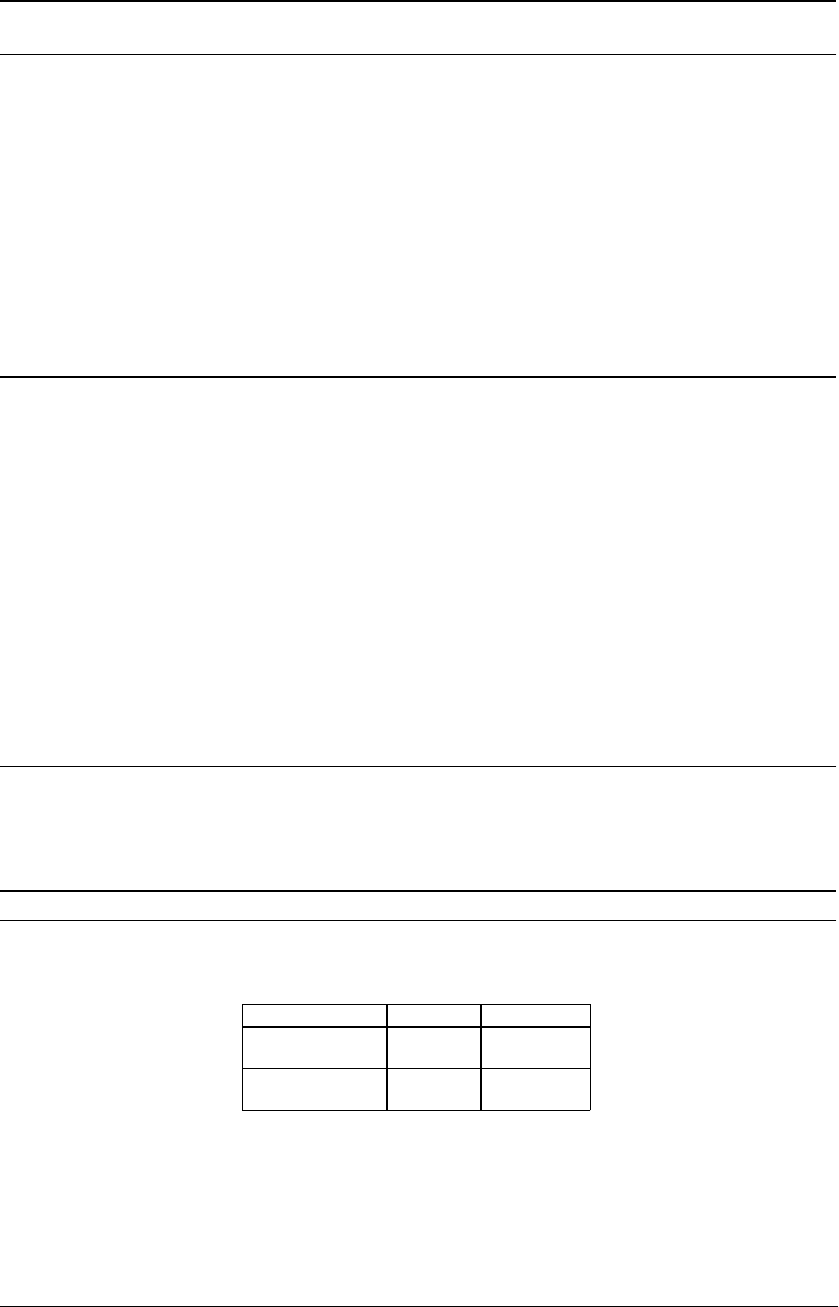

DTR, RTS: Modem control (D[1:0]) / Communications block modem control register (0x020002E)

For the communications macro select (MCRS) register (D[1:0]/0x0200000) setting of 00–that is, UART

communications mode–these bits drive the RTS and DTR output pins using positive logic. (See Table.)

Table 10.20 Communications Block Modem Control

Bit Setting Output Pin Output Level

RTS = 1

RTS = 0

RTS High

Low

DTR = 1

DTR = 0

DTR High

Low