II CORE BLOCK: ITC (Interrupt Controller)

B-II-5-10 EPSON S1C33210 FUNCTION PART

Interrupt after IDMA transfer

To generate an interrupt after completion of IDMA transfer:

The interrupt request that has been kept pending can be generated after completion of the DMA transfer.

In this case, the interrupt must be enabled by the IDMA control information (DINTEM = "1") in adition to the

interrupt controller and the PSR register settings.

However, if the transfer counter set for the selected IDMA channel does not reach the terminal count of 0 after

the number of transfers set have been performed, the interrupt factor flag is reset and no interrupt request is

generated. The transfer counter is decremented by 1 for each transfer performed.

If the transfer counter is decremented to 0 when DINTEN is set to "1", the interrupt factor flag is not reset and

the IDMA request bit is cleared to "0". An interrupt request is generated if other interrupt conditions are met.

The IDMA request bit must be set up again in order for IDMA to be invoked when an interrupt factor occurs

next time as well. To ensure that no unwanted IDMA request occurs, this setup must be performed after

resetting the interrupt factor flag.

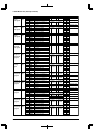

Figure 5.2 shows the hardware sequence when DINTEN is set to "1".

3 2 1 0

IDMA trigger (interrupt factor flag)

Transfer counter

Data transfer

Reset A signal

(reset interrupt factor flag)

Reset B signal

(reset IDMA request bit)

IDMA request bit

Interrupt request

Figure 5.2 Sequence when DINTEN = "1"

To disable an interrupt after completion of IDMA transfer:

If an interrupt has been disabled in the IDMA control information (DINTEN = "0"), the interrupt is not

generated since the interrupt factor flag is reset when the transfer counter becomes 0.

In this case, the IDMA request bit remains set to "1" without being cleared. However, the IDMA enable bit is

cleared, so the following IDMA request by the same interrupt factor will be disabled.

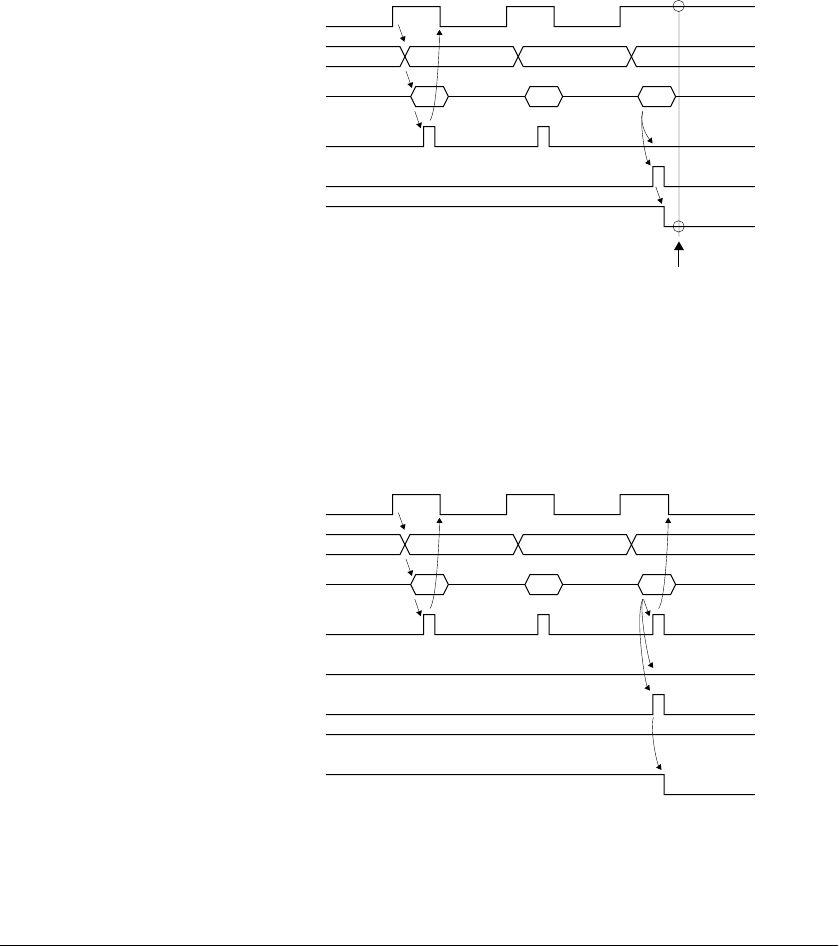

Figure 5.3 shows the hardware sequence when DINTEN is set to "0".

3 2 1 0

IDMA trigger (interrupt factor flag)

Transfer counter

Data transfer

Reset A signal

(reset interrupt factor flag)

Reset B signal

(reset IDMA request bit)

Reset C signal

(reset IDMA enable bit)

IDMA request bit

IDMA enable bit

L

"1"

Figure 5.3 Sequence when DINTEN = "0"

For details on IDMA, refer to "IDMA (Intelligent DMA)".