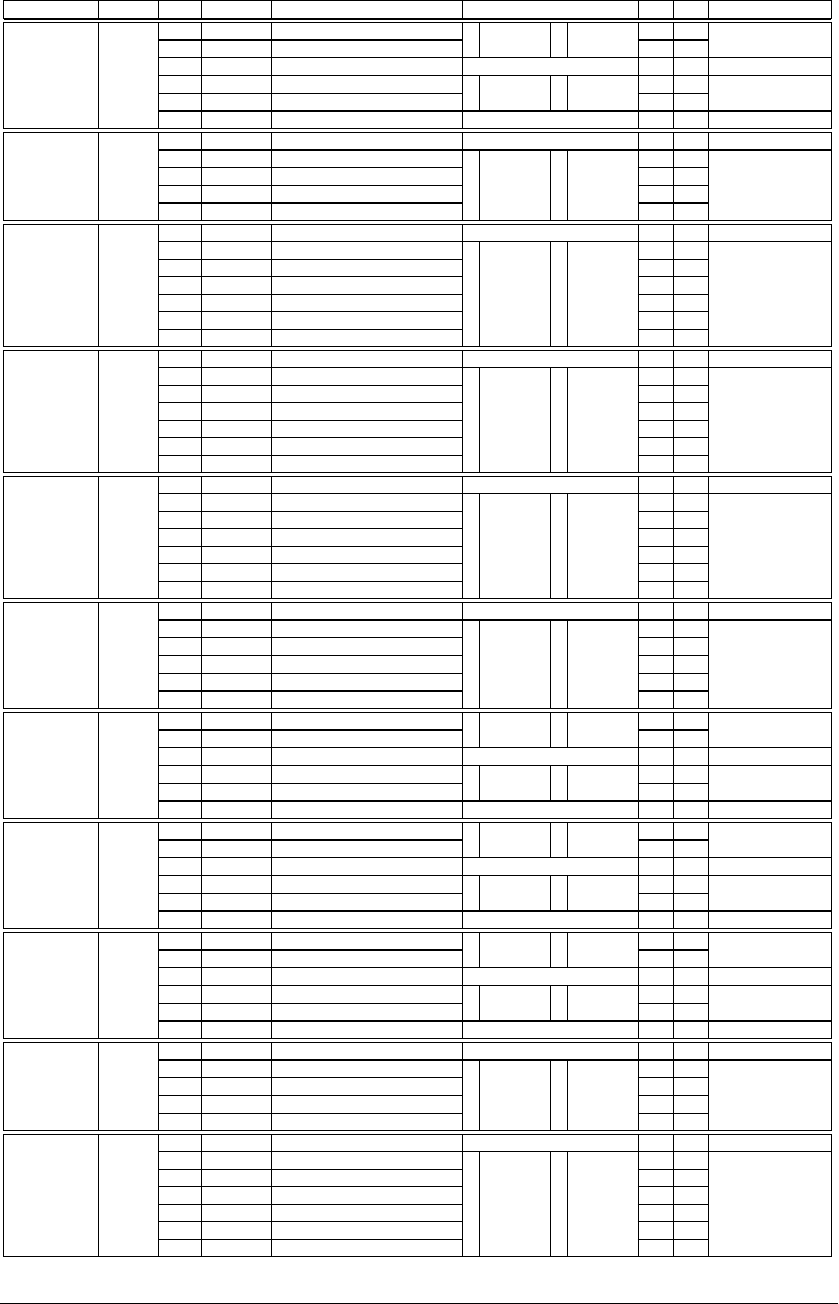

II CORE BLOCK: ITC (Interrupt Controller)

B-II-5-14 EPSON S1C33210 FUNCTION PART

NameAddressRegister name Bit Function Setting Init. R/W Remarks

E16TC5

E16TU5

–

E16TC4

E16TU4

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 5 comparison A

16-bit timer 5 comparison B

reserved

16-bit timer 4 comparison A

16-bit timer 4 comparison B

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040274

(B)

1 Enabled 0 Disabled

16-bit timer 4/5

interrupt

enable register

–

1 Enabled 0 Disabled

–

–

E8TU3

E8TU2

E8TU1

E8TU0

D7–4

D3

D2

D1

D0

reserved

8-bit timer 3 underflow

8-bit timer 2 underflow

8-bit timer 1 underflow

8-bit timer 0 underflow

– –

0

0

0

0

–

R/W

R/W

R/W

R/W

0 when being read.0040275

(B)

1 Enabled 0 Disabled

8-bit timer

interrupt

enable register

–

ESTX1

ESRX1

ESERR1

ESTX0

ESRX0

ESERR0

D7–6

D5

D4

D3

D2

D1

D0

reserved

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

SIF Ch.1 receive error

SIF Ch.0 transmit buffer empty

SIF Ch.0 receive buffer full

SIF Ch.0 receive error

– –

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040276

(B)

1 Enabled 0 Disabled

Serial I/F

interrupt

enable register

–

EP7

EP6

EP5

EP4

ECTM

EADE

D7–6

D5

D4

D3

D2

D1

D0

reserved

Port input 7

Port input 6

Port input 5

Port input 4

Clock timer

A/D converter

– –

0

0

0

0

0

0

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040277

(B)

1 Enabled 0 Disabled

Port input 4–7,

clock timer,

A/D interrupt

enable register

–

FK1

FK0

FP3

FP2

FP1

FP0

D7–6

D5

D4

D3

D2

D1

D0

reserved

Key input 1

Key input 0

Port input 3

Port input 2

Port input 1

Port input 0

– –

X

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040280

(B)

1 Factor is

generated

0 No factor is

generated

Key input,

port input 0–3

interrupt factor

flag register

–

FIDMA

FHDM3

FHDM2

FHDM1

FHDM0

D7–5

D4

D3

D2

D1

D0

reserved

IDMA

High-speed DMA Ch.3

High-speed DMA Ch.2

High-speed DMA Ch.1

High-speed DMA Ch.0

– –

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

0 when being read.0040281

(B)

DMA interrupt

factor flag

register

1 Factor is

generated

0 No factor is

generated

F16TC1

F16TU1

–

F16TC0

F16TU0

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 1 comparison A

16-bit timer 1 comparison B

reserved

16-bit timer 0 comparison A

16-bit timer 0 comparison B

reserved

X

X

–

X

X

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040282

(B)

1 Factor is

generated

0 No factor is

generated

16-bit timer 0/1

interrupt factor

flag register

–

1 Factor is

generated

0 No factor is

generated

–

F16TC3

F16TU3

–

F16TC2

F16TU2

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 3 comparison A

16-bit timer 3 comparison B

reserved

16-bit timer 2 comparison A

16-bit timer 2 comparison B

reserved

X

X

–

X

X

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040283

(B)

1 Factor is

generated

0 No factor is

generated

16-bit timer 2/3

interrupt factor

flag register

–

1 Factor is

generated

0 No factor is

generated

–

F16TC5

F16TU5

–

F16TC4

F16TU4

–

D7

D6

D5–4

D3

D2

D1–0

16-bit timer 5 comparison A

16-bit timer 5 comparison B

reserved

16-bit timer 4 comparison A

16-bit timer 4 comparison B

reserved

X

X

–

X

X

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0040284

(B)

1 Factor is

generated

0 No factor is

generated

16-bit timer 4/5

interrupt factor

flag register

–

1 Factor is

generated

0 No factor is

generated

–

–

F8TU3

F8TU2

F8TU1

F8TU0

D7–4

D3

D2

D1

D0

reserved

8-bit timer 3 underflow

8-bit timer 2 underflow

8-bit timer 1 underflow

8-bit timer 0 underflow

– –

X

X

X

X

–

R/W

R/W

R/W

R/W

0 when being read.0040285

(B)

1 Factor is

generated

0 No factor is

generated

8-bit timer

interrupt factor

flag register

–

FSTX1

FSRX1

FSERR1

FSTX0

FSRX0

FSERR0

D7–6

D5

D4

D3

D2

D1

D0

reserved

SIF Ch.1 transmit buffer empty

SIF Ch.1 receive buffer full

SIF Ch.1 receive error

SIF Ch.0 transmit buffer empty

SIF Ch.0 receive buffer full

SIF Ch.0 receive error

– –

X

X

X

X

X

X

–

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.0040286

(B)

1 Factor is

generated

0 No factor is

generated

Serial I/F

interrupt factor

flag register