II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-28 EPSON S1C33210 FUNCTION PART

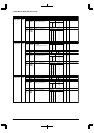

DRAM random write cycle

Example: RAS: 1 cycle; CAS: 2 cycles; Precharge: 1 cycle

BCLK

A[11:0]

#RASx

#HCAS/

#LCAS

#WE

D[15:0]

ROW COL

write data

RAS cycle CAS cycle

Precharge

cycle

Figure 4.32 2CAS Type DRAM Random Write Cycle

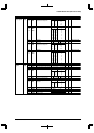

DRAM write cycle (fast page or EDO page mode)

Example: RAS: 1 cycle; CAS: 2 cycles; Precharge: 1 cycle; word-write sample

ROW COL #1 COL #2

write data

RAS cycle CAS cycle #1 CAS cycle #2

Precharge

cycle

BCLK

A[11:0]

#RASx

#HCAS/

#LCAS

#WE

D[15:0]

write data

Figure 4.33 DRAM Word-Write Cycle (fast page or EDO page mode)

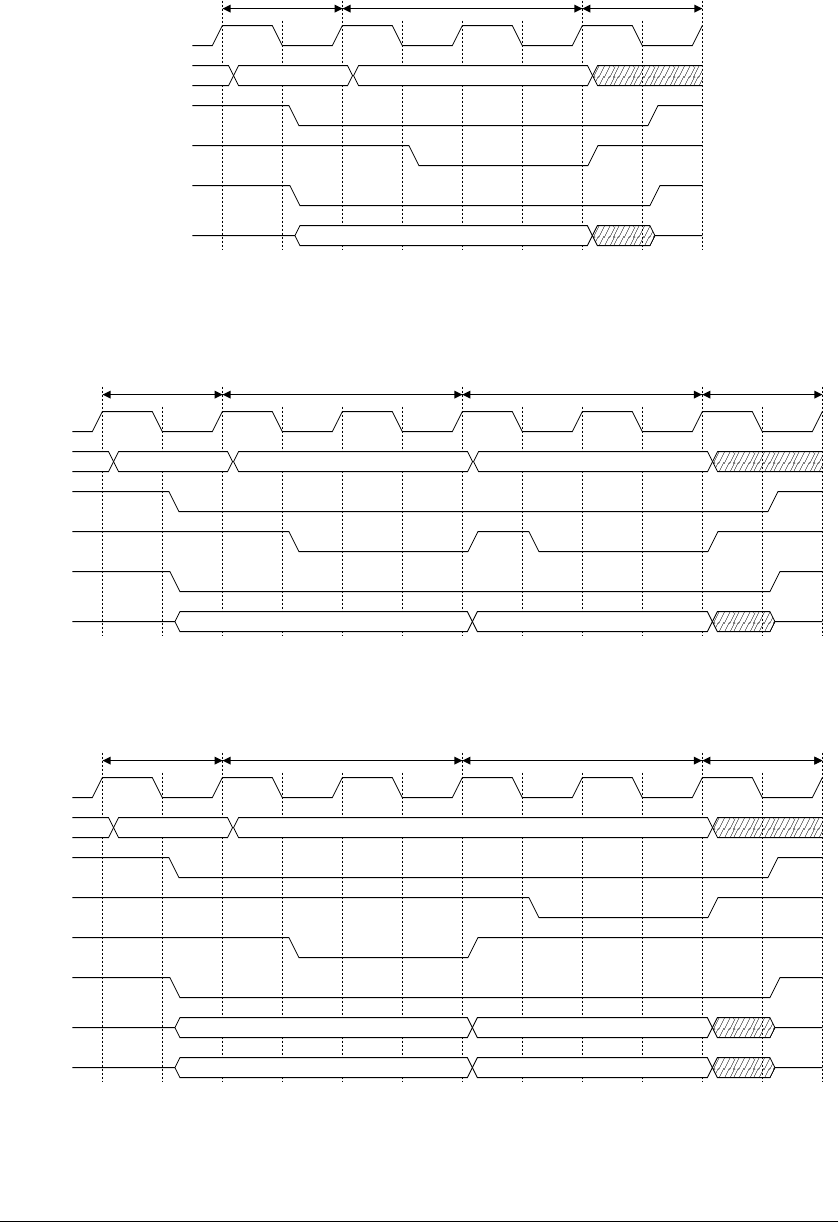

Example: RAS: 1 cycle; CAS: 2 cycles; Precharge: 1 cycle; byte-write sample (little endian)

ROW COL

write data

BCLK

A[11:0]

#RASx

#HCAS

#LCAS

#WE

D[15:8]

D[7:0]

Undefined

Undefinedwrite data

RAS cycle CAS cycle #1 CAS cycle #2

Precharge

cycle

Figure 4.34 DRAM Byte-Write Cycle (fast page or EDO page mode)