II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-36 EPSON S1C33210 FUNCTION PART

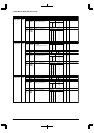

NameAddressRegister name Bit Function Setting Init. R/W Remarks

1 Successive 0 Normal

–

–

CEFUNC1

CEFUNC0

CRAS

RPRC1

RPRC0

–

CASC1

CASC0

–

RASC1

RASC0

DF–C

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

reserved

reserved

#CE pin function selection

Successive RAS mode setup

DRAM

RAS precharge cycles selection

reserved

DRAM

CAS cycles selection

reserved

DRAM

RAS cycles selection

– –

–

0

0

0

0

0

–

0

0

–

0

0

–

–

R/W

R/W

R/W

–

R/W

–

R/W

0 when being read.

Undefined when read.

0 when being read.

0 when being read.

0048130

(HW)

1

0

0

x

1

0

CFFUNC[1:0]

#CE output

#CE7/8..#CE17/18

#CE6..#CE17

#CE4..#CE10

1

1

0

0

1

0

1

0

RPRC[1:0] Number of cycles

4

3

2

1

–

1

1

0

0

1

0

1

0

CASC[1:0] Number of cycles

4

3

2

1

–

1

1

0

0

1

0

1

0

RASC[1:0] Number of cycles

4

3

2

1

DRAM timing

set-up register

–

–

1 Internal

access

0 External

access

1 Internal

access

0 External

access

1 Big endian 0

Little endian

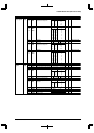

A18IO

A16IO

A14IO

A12IO

–

A8IO

A6IO

A5IO

A18EC

A16EC

A14EC

A12EC

A10EC

A8EC

A6EC

A5EC

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Area 18, 17 internal/external access

Area 16, 15 internal/external access

Area 14, 13 internal/external access

Area 12, 11 internal/external access

reserved

Area 8, 7 internal/external

access

Area 6 internal/external

access

Area 5, 4 internal/external

access

Area 18, 17 endian control

Area 16, 15 endian control

Area 14, 13 endian control

Area 12, 11 endian control

Area 10, 9 endian control

Area 8, 7 endian control

Area 6 endian control

Area 5, 4 endian control

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0 when being read.

0048132

(HW)

Access control

register

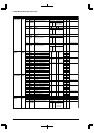

–

1 Enabled 0 Disabled

1 Enabled 0 Disabled

A18AS

A16AS

A14AS

A12AS

–

A8AS

A6AS

A5AS

A18RD

A16RD

A14RD

A12RD

–

A8RD

A6RD

A5RD

DF

DE

DD

DC

DB

DA

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

Area 18, 17 address strobe signal

Area 16, 15 address strobe signal

Area 14, 13 address strobe signal

Area 12, 11 address strobe signal

reserved

Area 8, 7 address strobe signal

Area 6 address strobe signal

Area 5, 4 address strobe signal

Area 18, 17 read signal

Area 16, 15 read signal

Area 14, 13 read signal

Area 12, 11 read signal

reserved

Area 8, 7 read signal

Area 6 read signal

Area 5, 4 read signal

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

R/W

R/W

R/W

R/W

–

R/W

R/W

R/W

0 when being read.

0 when being read.

0048138

(HW)

G/A read signal

control register

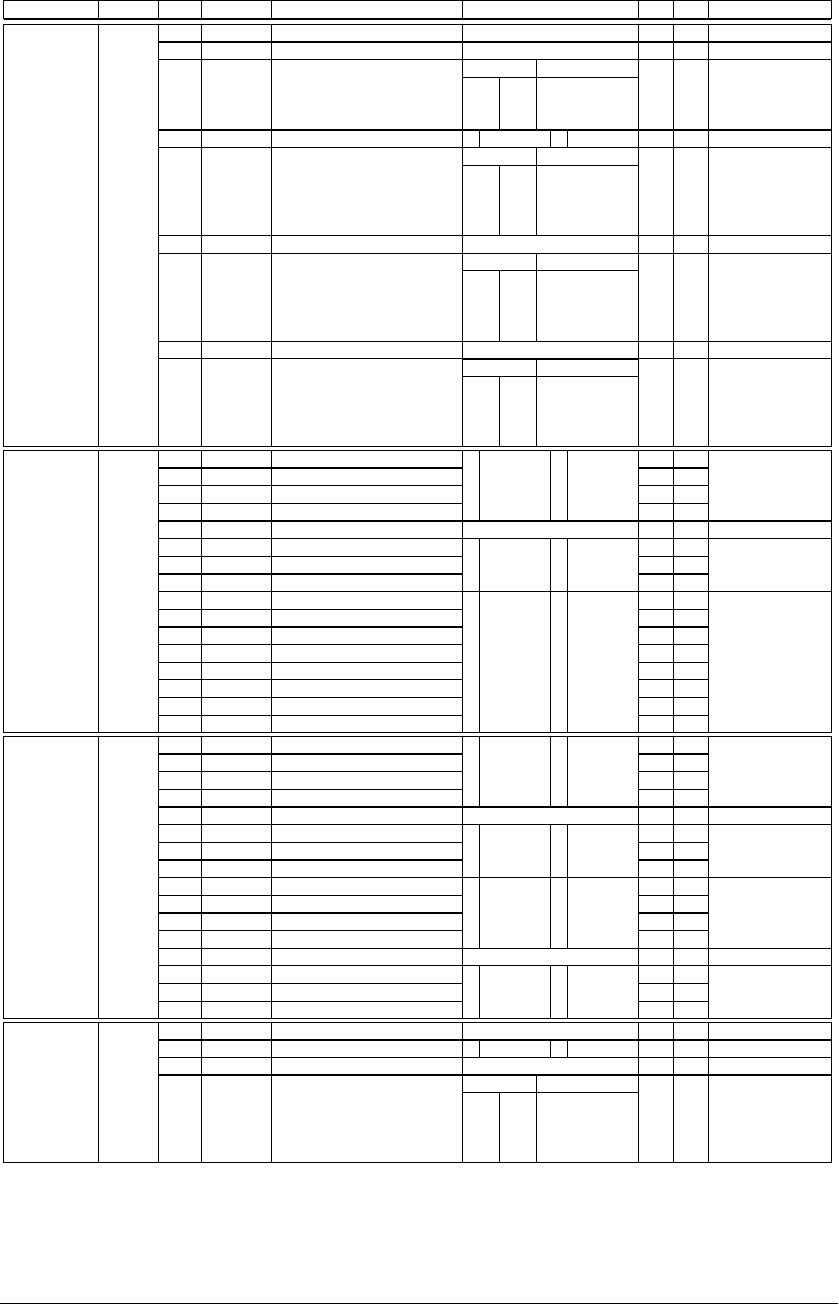

–

1 Enabled 0 Disabled

1 Enabled 0 Disabled

–

A1X1MD

–

BCLKSEL1

BCLKSEL0

D7–4

D3

D2

D1

D0

reserved

Area 1 access-speed

reserved

BCLK output clock selection

1

1

0

0

1

0

1

0

BCLKSEL[1:0]

–

–

BCLK

PLL_CLK

OSC3_CLK

BCU_CLK

CPU_CLK

0

0

0

0

0

–

R/W

–

R/W

0 when being read.

x2 speed mode only

0 when being read.

004813A

(B)

BCLK select

register

1 2 cycles 0 4 cycles