II CORE BLOCK: BCU (Bus Control Unit)

B-II-4-30 EPSON S1C33210 FUNCTION PART

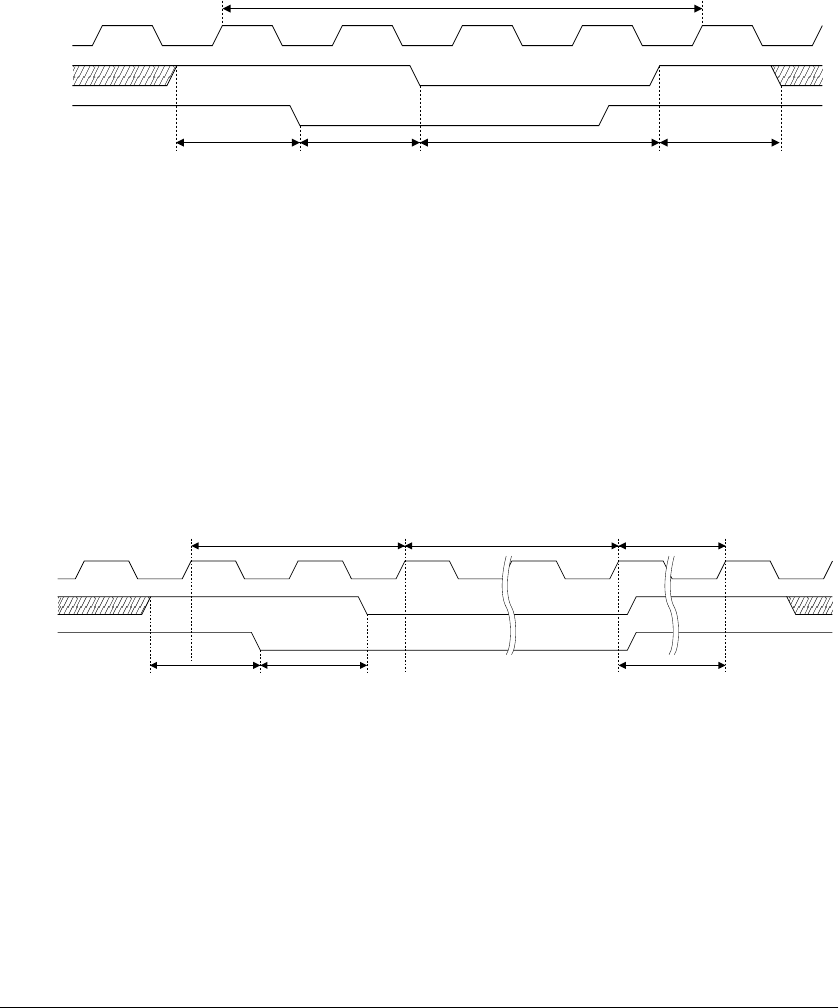

DRAM Refresh Cycles

The DRAM interface supports a CAS-before-RAS refresh cycle and a self-refresh cycle.

CAS-before-RAS refresh cycle

Before performing a CAS-before-RAS refresh, set RPC2 to "1" while RPC1 = "0" in order to enable the

DRAM refresh function. Once this is done, the BCU executes a CAS-before-RAS refresh by using the

underflow signal that is output by the 8-bit programmable timer 0 as a trigger. Therefore, refresh generation

timing can be programmed using the internal prescaler and 8-bit programmable timer 0.

For details on how to control the prescaler and 8-bit programmable timer 0, refer to "Prescaler and Operating

Clock for Peripheral Circuits", and "8-Bit Programmable Timers".

Example: RPC delay: 1 cycle; Refresh RAS pulse width: 2 cycles; Precharge: 1 cycle

CAS-before-RAS refresh cycle

Refresh

RPC delay

Fixed at

1 cycle

Refresh

RPC pulse width

Precharge

cycle

BCLK

#RAS

#HCAS/

#LCAS

Figure 4.36 CAS-Before-RAS Refresh

When the refresh cycle is terminated, the #HCAS/#LCAS signal boot timing is 0.5 cycles before that of #RAS.

Consequently, the pulse width of #HCAS/#LCAS is determined by the refresh RAS pulse width that was set

using RRA. The number of precharge cycles after the refresh cycle is defined by the value that was set using

RPRC, the same value that is used for both random cycles and page mode accesses.

Self-refresh

To support DRAM chips equipped with a self-refresh function, the BCU has a function to generate a self-

refresh cycle.

To start a self-refresh cycle, set RPC2 to "1" after setting RPC1 to "1". To deactivate a self-refresh cycle, write

"0" to RPC1 or RPC2.

Example: RPC delay: 1 cycle

Self-refresh mode set up

Self-refresh mode

deactivationSelf-refresh mode

Refresh

RPC delay

Fixed at

1 cycle

Precharge cycle

(6 cycles)

BCLK

#RAS

#HCAS/

#LCAS

Figure 4.37 Self-Refresh

For a self-refresh function as well, the RPC delay is determined by setting RPC0 in the same way as for a

CAS-before-RAS refresh.

The refresh RAS pulse width is determined by the timing at which the refresh is deactivated in software and is

unaffected by settings of RRA.

#RAS and #HCAS/#LCAS are booted up simultaneously upon completion of a self-refresh and the precharge

duration that follows is fixed at 6 cycles.