IV ANALOG BLOCK: A/D CONVERTER

S1C33210 FUNCTION PART EPSON B-IV-2-11

ADD9–ADD0: A/D converted data (D[1:0]) / A/D conversion result (high-order) register (0x40241)

(D[7:0]) / A/D conversion result (low-order) register (0x40240)

Stores the results of A/D conversion.

The LSB is stored in ADD0, and the MSB is stored in ADD9. ADD0 and ADD1 are mapped to bits D0 and D1 at

the address 0x40241, but bits D2 through D7 are always 0 when read.

This is a read-only register, so writing to this register is ignored.

At initial reset, the data in this register is cleared to "0".

MS: A/D conversion mode selection (D5) / A/D trigger register (0x40242)

Selects an A/D conversion mode.

Write "1": Continuous mode

Write "0": Normal mode

Read: Valid

The A/D converter is set for the continuous mode by writing "1" to MS. In this mode, A/D conversions in the range

of the channels selected using CS and CE are executed continuously until stopped in the software.

When MS = "0", the A/D converter operates in the normal mode. In this mode, A/D conversion is completed after all

inputs in the range of the channels selected by CS and CE are converted in one operation.

At initial reset, MS is set to "0" (normal mode).

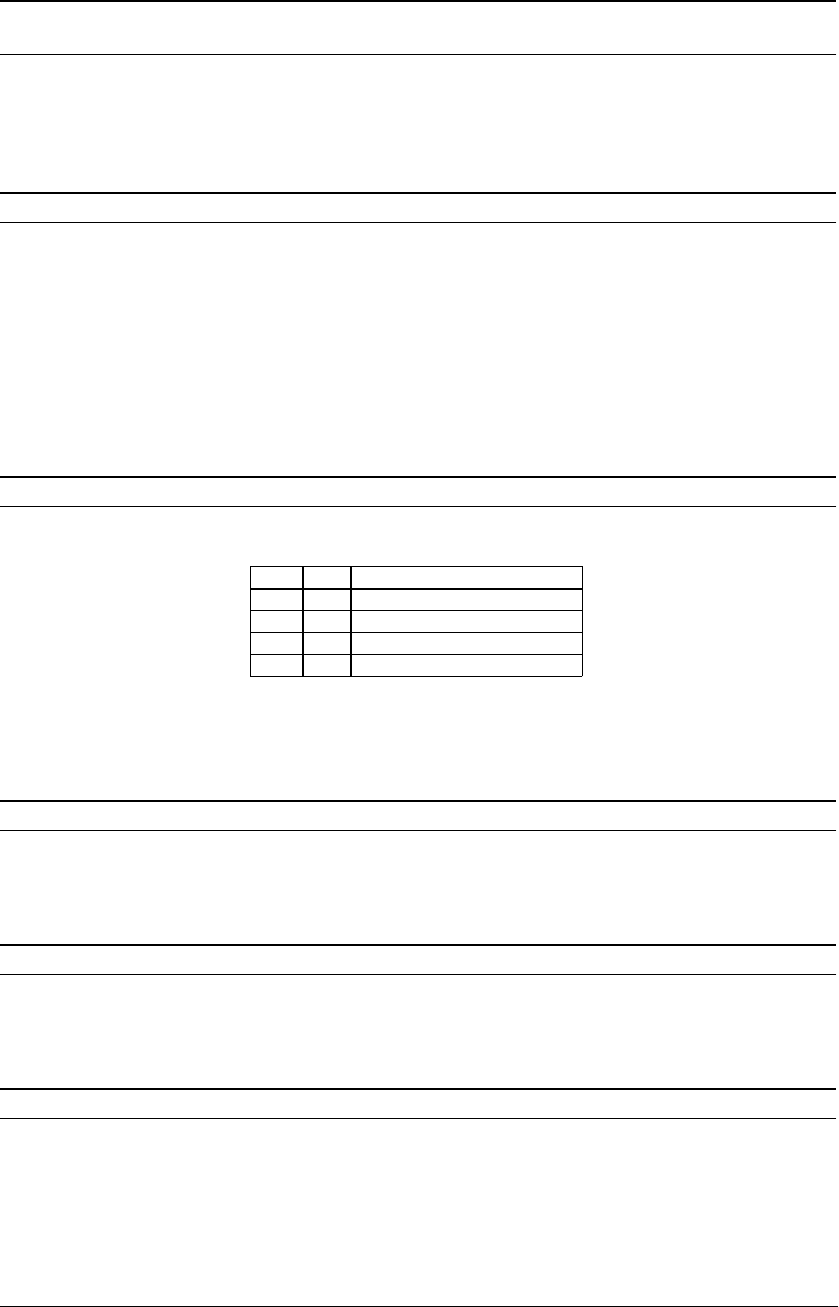

TS1–TS0: Trigger selection (D[4:3]) / A/D trigger register (0X40242)

Selects a trigger to start A/D conversion.

Table 2.7 Trigger Selection

TS1 TS0 Trigger

1 1 External trigger (K52/#ADTRG)

1 0 8-bit programmable timer 0

0 1 16-bit programmable timer 0

0 0 Software

When an external trigger is used, use the CFK52 bit to set the K52 pin for #ADTRG.

When a programmable timer is used, since its underflow signal (8-bit timer) or comparison match B signal (16-bit

timer) serves as a trigger, set the cycle and other parameters for the programmable timer.

At initial reset, TS is set to "0" (software trigger).

CH2–CH0: Conversion channel status (D[2:0]) / A/D trigger register (0X40242)

Indicates the channel number (0 to 3) currently being A/D-converted.

When A/D conversion is performed in multiple channels, read this bit to identify the channel in which conversion is

underway.

At initial reset, CH is set to "0" (AD0).

CE2–CE0: Conversion end-channel setup (D[5:3]) / A/D channel register (0x40243)

Sets the conversion end channel by selecting a channel number from 0 to 3.

Analog inputs can be A/D-converted successively from the channel set using CS to the channel set using this bit in

one operation. If only one channel is to be A/D converted, set the same channel number in both the CS and CE bits.

At initial reset, CE is set to "0" (AD0).

CS2–CS0: Conversion start-channel setup (D[2:0]) / A/D channel register (0x40243)

Sets the conversion start channel by selecting a channel number from 0 to 3.

Analog inputs can be A/D-converted successively from the channel set using this bit to the channel set using CE in

one operation. If only one channel is to be A/D converted, set the same channel number in both the CS and CE bits.

At initial reset, CS is set to "0" (AD0).