Architecture

110

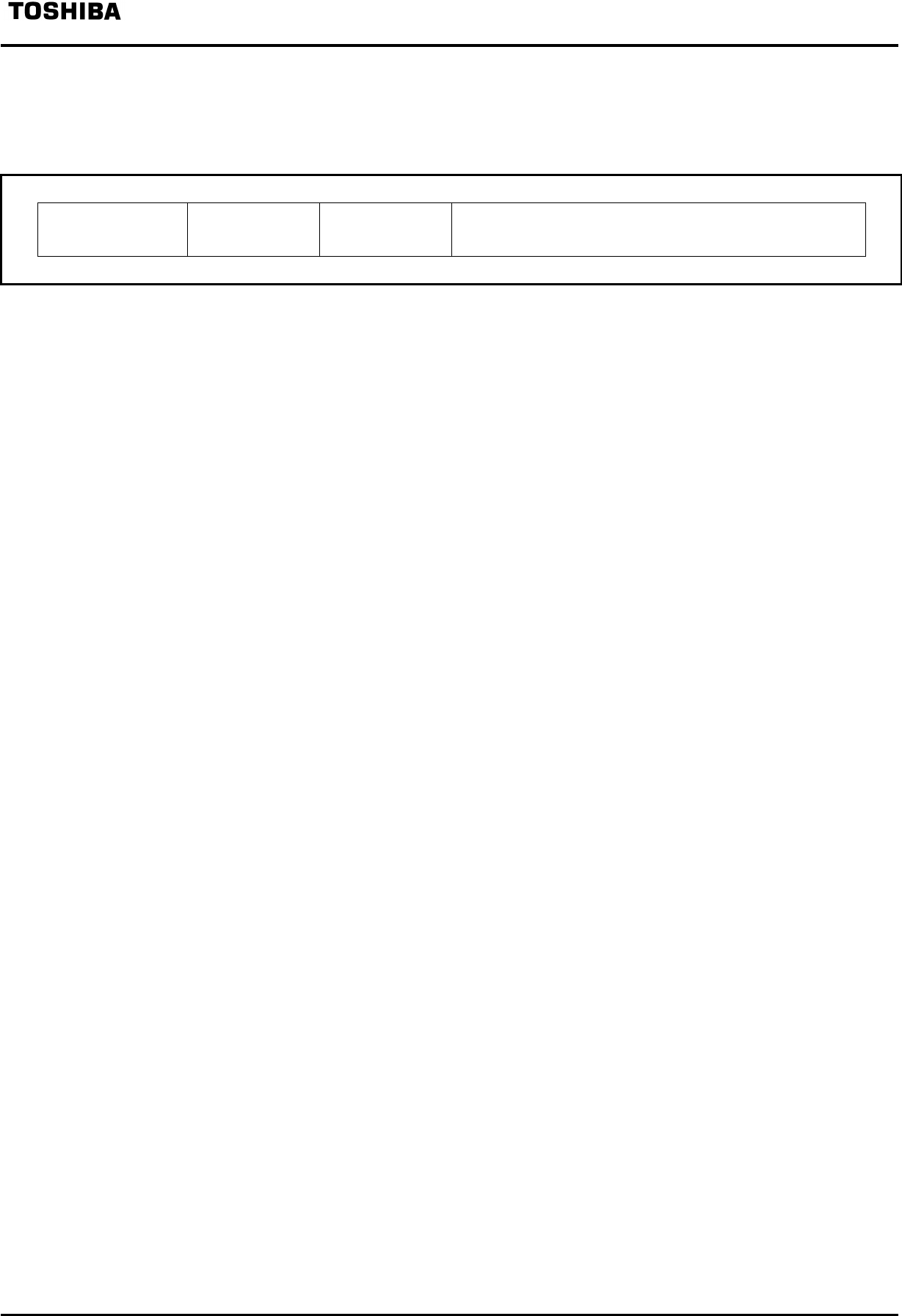

BCzFL Branch On Coprocessor z False Likely BCzFL

31 26 25 21 20 16 15 0

COPz

0100xx*

BC

01000

BCFL

00010

offset

6 5 5 16

Format :

BCzFL offset

Description :

Generates a branch target address by adding the address of the instruction in the delay slot to the 16-

bit offset (that has been left-shifted two bits and sign-extended to 32 bits). If the coprocessor z

condition (CPCOND) sampled during execution of the immediately preceding instruction is false,

the program branches to the target address after a one-cycle delay. If the condition is true, the

instruction in the delay slot is treated as a NOP.

*Refer also to the table on the following page (Operation Code Bit Encoding) or to the section

entitled “Bit Encoding of CPU Instruction Opcodes” at the end of this appendix.