Architecture

28

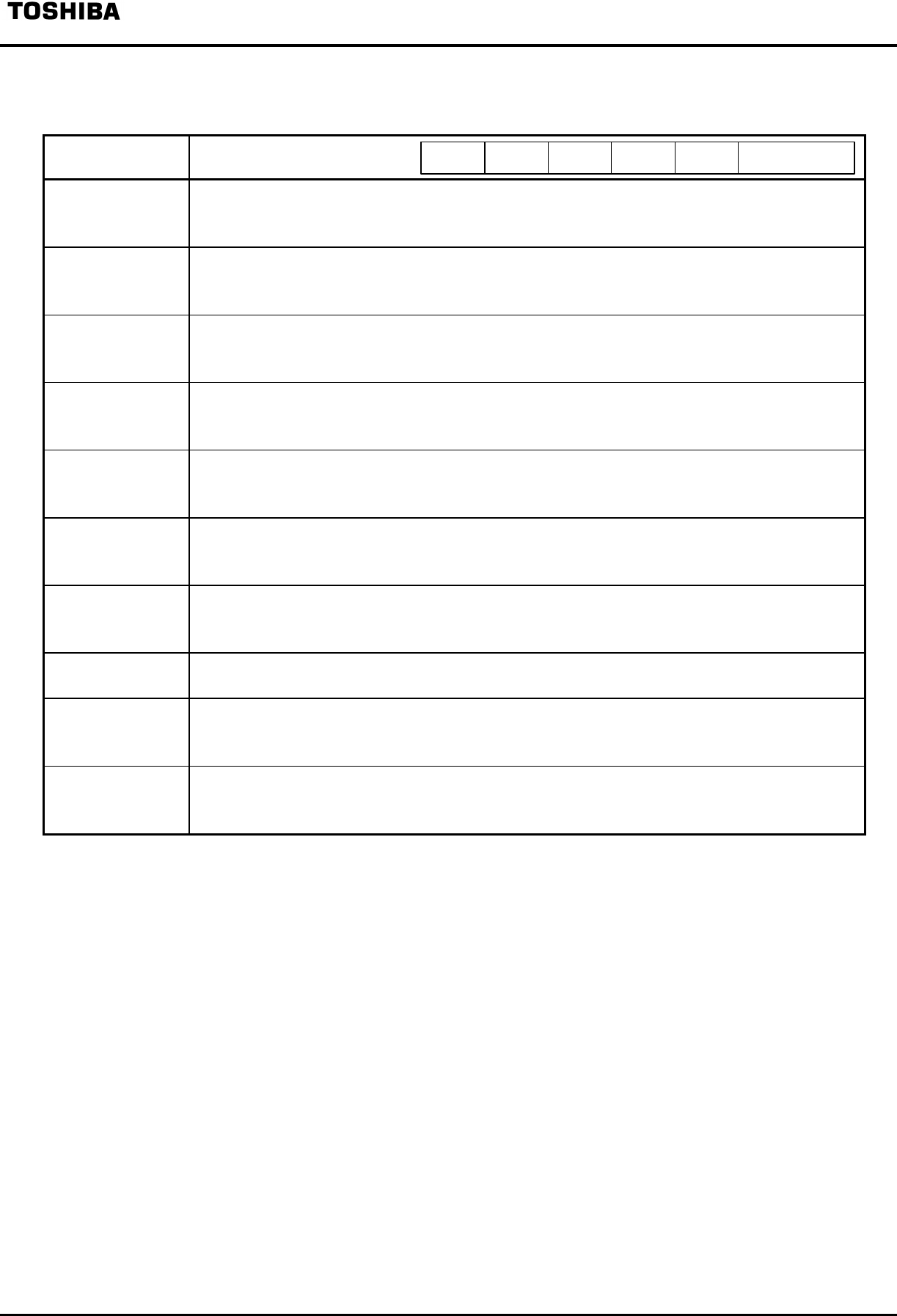

Table 3-5. Three-operand register-type instructions

Instruction Format and Description

Add ADD rd, rs, rt

Add the contents of registers rs and rt, and store the result in register rd. An

exception is raised in the event of a two’s-complement overflow.

Add Unsigned ADDU rd, rs, rt

Add the contents of registers rs and rt, and store the result in register rd. No

exception is raised on a two’s-complement overflow.

Subtract SUB rd, rs, rt

Subtract the contents of register rt from rs, and store the result in register rd.

An exception is raised in the event of a two’s-complement overflow.

Subtract

Unsigned

SUBU rd, rs, rt

Subtract the contents of register rt from rs, and store the result in register rd.

No exception is raised on a two’s-complement overflow.

Set on Less

Than

SLT rd, rs, rt

Compare the contents of registers rt and rs as 32-bit signed integers. If rs is

less than rt, store 1 in rd as the result; otherwise store 0 in rd.

Set on Less

Than Unsigned

SLTU rd, rs, rt

Compare the contents of registers rt and rs as 32-bit unsigned integers. If rs is

less than rt, store 1 in rd as the result; otherwise store 0 in rd.

AND AND rd, rs, rt

Bitwise AND the contents of registers rs and rt, and store the result in register

rd.

OR OR rd, rs, rt

Bitwise OR the contents of registers rs and rt, and store the result in register rd.

Exclusive OR XOR rd, rs, rt

Bitwise Exclusive-OR the contents of registers rs and rt, and store the result in

register rd.

NOR NOR rd, rs, rt

Bitwise NOR the contents of registers rs and rt, and store the result in register

rd.

rtrs funct0op rd