Architecture

36

3.7 Coprocessor Instructions

Coprocessor instructions invoke coprocessor operations. The format of these instructions depends on which

coprocessor is used.

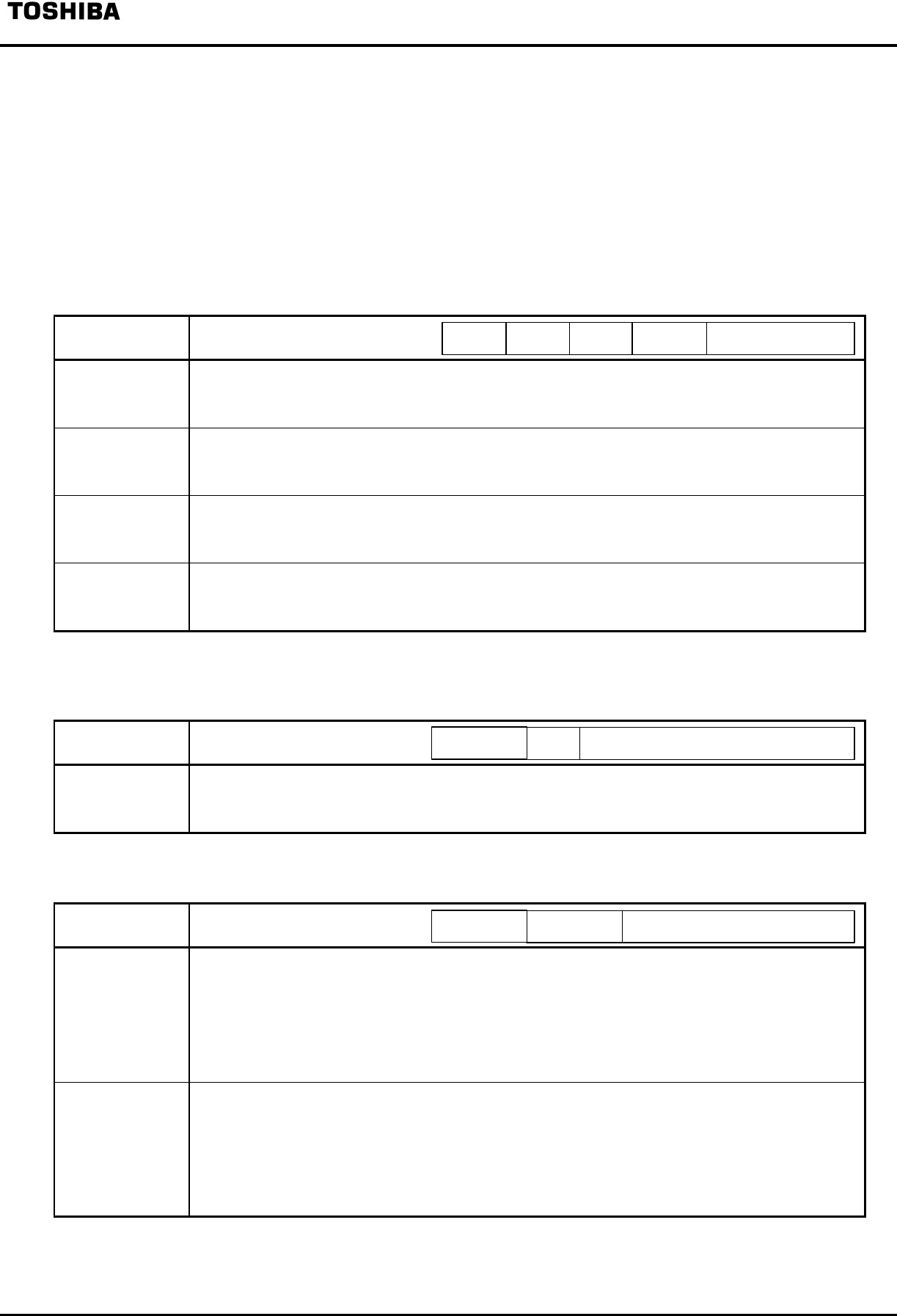

Table 3-12. Coprocessor instructions

(a) MTCz, MFCz, CTCz, CFCz

Instruction Format and Description

Move To

Coprocessor

MTCz rt, rd

Move the contents of CPU general register rt to coprocessor z’s coprocessor

register rd.

Move From

Coprocessor

MFCz rt, rd

Move the contents of coprocessor z’s coprocessor register rd to CPU general

register rt.

Move Control

To

Coprocessor

CTCz rt, rd

Move the contents of CPU general register rt to coprocessor z’s coprocessor

control register rd.

Move Control

From

Coprocessor

CFCz rt, rd

Move the contents of coprocessor z’s coprocessor control register rd to CPU

general register rt.

(b) COPz

Instruction Format and Description

Coprocessor

Operation

COPz cofun

Execute in coprocessor z the processing indicated in cofun. The CPU state is

not changed by the processing executed in the coprocessor.

(c) BCzT, BCzF

Instruction Format and Description

Branch on

Coprocessor

z True

BCzT offset

Generate the branch target address by adding the address of the instruction in

the delay slot (the instruction to be executed during the branch) and the 16-bit

offset (after left-shifting two bits and sign-extending to 32 bits). If the

coprocessor z condition line is true, branch to the target address after a one-

cycle delay.

Branch on

Coprocessor

z False

BCzF offset

Generate the branch target address by adding the address of the instruction in

the delay slot (the instruction to be executed during the branch) and the 16-bit

offset (after left-shifting two bits and sign-extending to 32 bits). If the

coprocessor z condition line is false, branch to the target address after a one-

cycle delay.

rtfunct 0

cofun

offset

rd

co

funct

op

op

op