Architecture

172

SB Store Byte SB

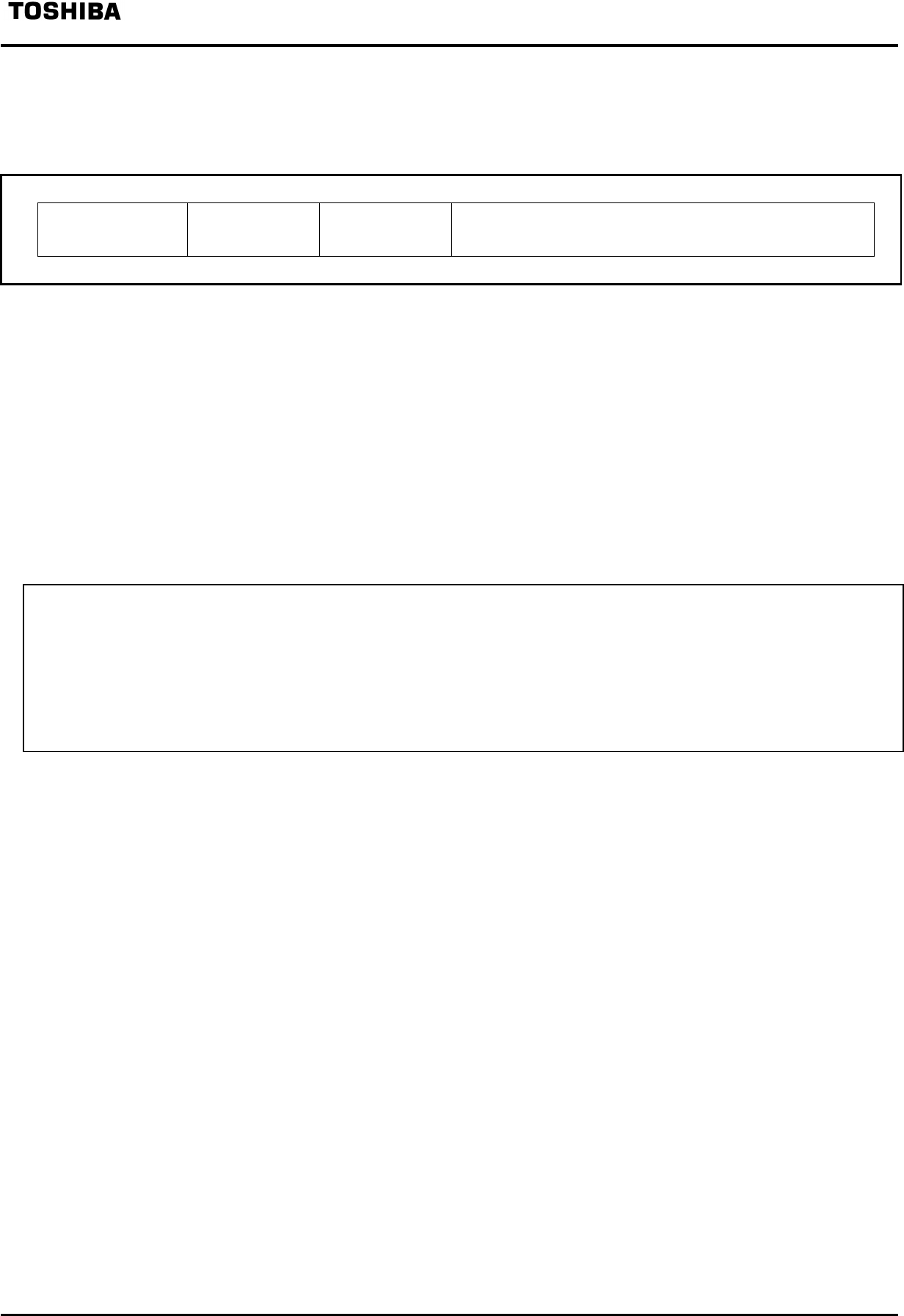

31 26 25 21 20 16 15 0

SB

101000

base rt offset

6 5 5 16

Format :

SB rt, offset(base)

Description :

Generates a 32-bit effective address by sign-extending the 16-bit offset and adding it to the contents

of general-purpose register base. It then stores the least significant byte of register rt at the resulting

effective address.

Operation :

T:

vAddr ← ((offset

15

)

16

||

offset

15..0

)

+ GPR[base]

(pAddr, uncached) ← AddressTranslation (vAddr, DATA)

pAddr ← pAddr

31..2

|| (pAddr

1..0

xor ReverseEndian

2

)

byte ← vAddr

1..0

xor BigEndianCPU

2

data ←GPR[rt]

31-8*byte..0

|| 0

8*byte

StoreMemory (uncached, BYTE, data, pAddr, vAddr, DATA)

Exceptions :

UTLB Refill exception (reserved)

TLB Refill exception (reserved)

TLB Modified exception (reserved)

Address Error exception