Architecture

127

BLTZAL Branch On Less Than Zero And Link BLTZAL

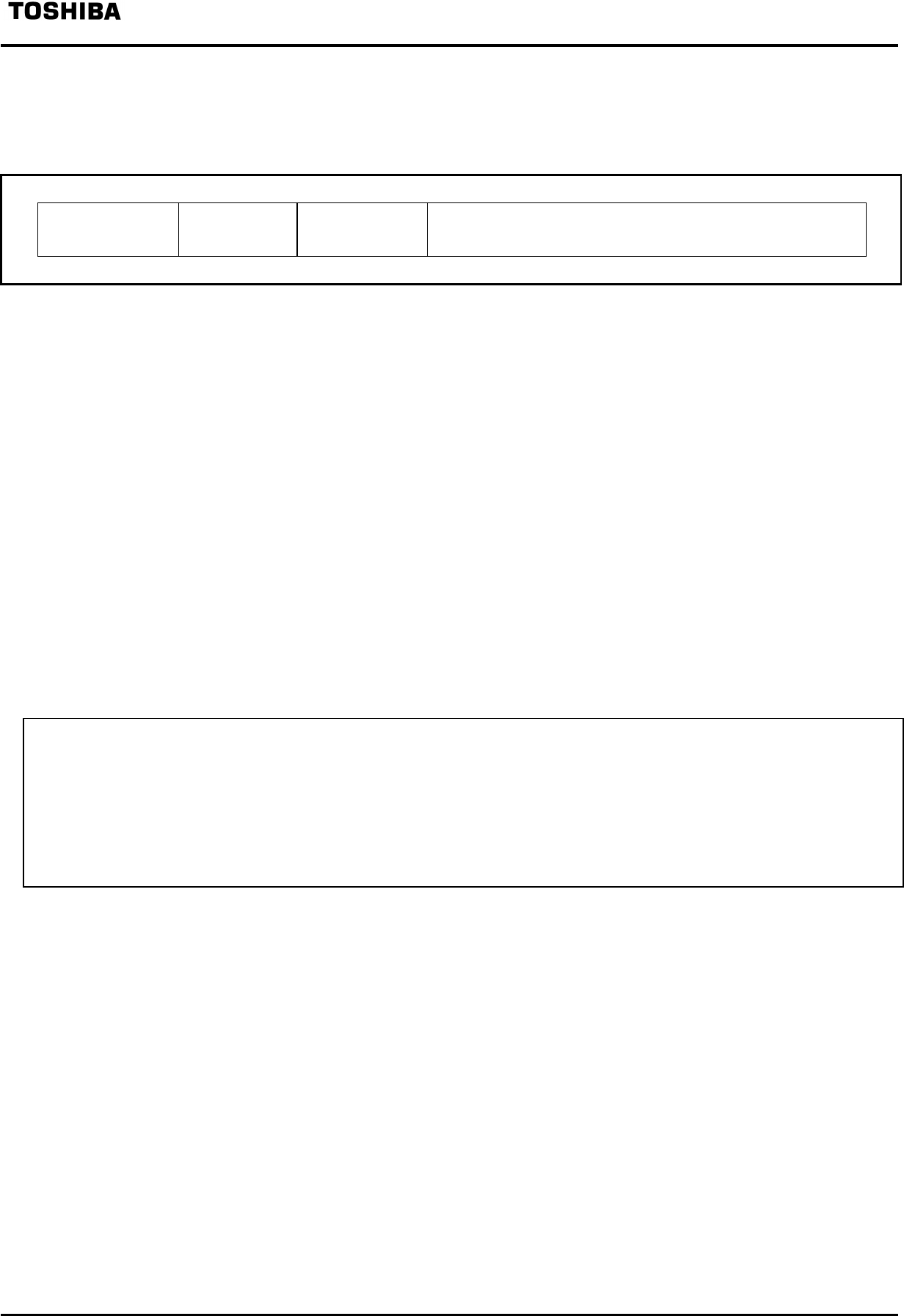

31 26 25 21 20 16 15 0

BCOND

000001

rs

BLTZAL

10000

offset

6 5 5 16

Format :

BLTZAL rs, offset

Description :

Generates a branch target address by adding the address of the instruction in the delay slot to the 16-

bit offset (that has been left-shifted two bits and sign-extended to 32 bits). The address of the

instruction following the instruction in the delay slot is unconditionally placed in link register r31 as

the return address from the branch. If the value in general-purpose register rs is negative (i.e., the

sign bit of rs is 1), the program branches to the target address after a one-cycle delay.

Register r31 should not be used for rs, as this would prevent the instruction from restarting.

However, if this is done it is not trapped as an error.

Operation :

T:

T + 1:

target ← (offset

15

)

14

|| offset || 0

2

condition ← (GPR[rs]

31

= 1)

GPR[31] ← PC + 8

if condition then

PC ← PC + target

endif

Exceptions :

None