Architecture

32

3.5 Jump/Branch Instructions

Jump/branch instructions change the program flow. A jump/branch instruction will delay the pipeline by one

instruction cycle, however, an instruction inserted into the delay slot (immediately following a branch

instruction) can be executed while the instruction at the branch target address is being fetched.

Jump and Jump And Link instructions, typically used to call subroutines, have the J-type instruction format.

The jump target address is generated as follows. The 26-bit target address (target) of the instruction is left-

shifted two bits and combined with the high-order four bits of the current PC (program counter) value to form

a 32-bit absolute address. This becomes the branch target address of the jump instruction. The PC shows

the address of the branch delay slot at that time.

The Jump And Link instruction puts the return address in register r31.

The R-type instruction format is used for returns from subroutines and long-distance jumps beyond one page

(Jump Register and Jump And Link Register instructions). The register value in this format is a 32-bit byte

address.

Branch instructions use the I-type format. Branching is to an relative address determined by adding a 16-bit

signed offset to the program counter.

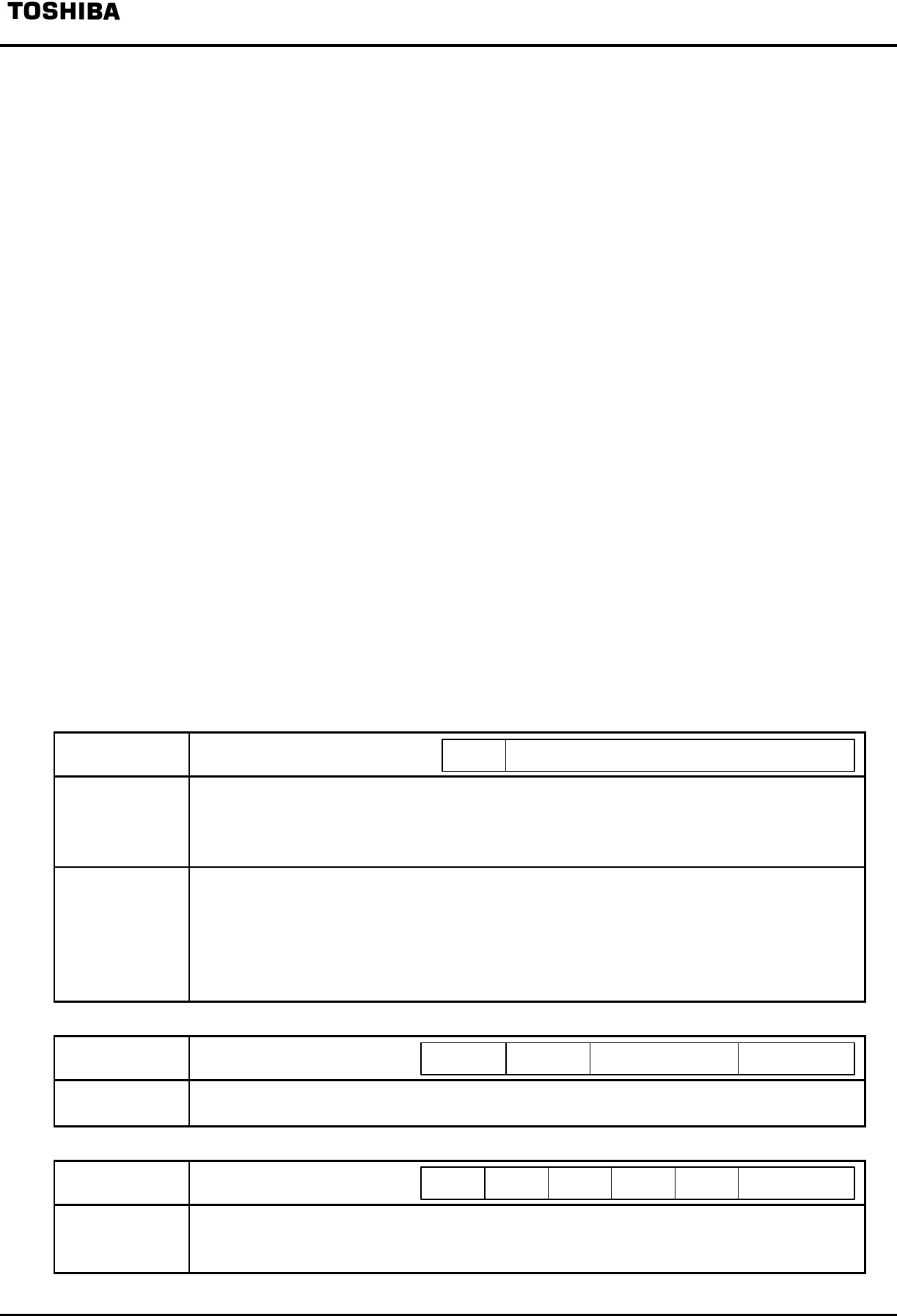

Table 3-9. Jump instructions

(a) J, JAL

Instruction Format and Description

Jump J target

Left-shift the 26-bit target by two bits and, after a one-instruction delay, jump to

an address formed by combining this result with the high-order 4 bits of the

program counter (PC).

Jump And

Link

JAL target

Left-shift the 26-bit target by two bits and, after a one-instruction delay, jump to

an address formed by combining the result with the high-order 4 bits of the

program counter (PC). Store in r31 (link register) the address of the

instruction following the instruction in the delay slot (The instruction in the delay

slot is executed during the jump).

(b) JR

Instruction Format and Description

Jump

Register

JR rs

Jump to the address in register rs after a one-instruction delay.

(c) JALR

Instruction Format and Description

Jump And

Link

Register

JALR rs, rd

Jump to the address in register rs after a one-instruction delay. Store in rd the

address of the instruction following the instruction in the delay slot (the

0

op

rs

rd

funct

funct

target

0

0

op

op rd