Architecture

190

SWR Store Word Right SWR

31 26 25 21 20 16 15 0

SWR

101110

base rt offset

6 5 5 16

Format :

SWR rt, offset(base)

Description :

Used together with SWL to store the contents of a register into four consecutive bytes of memory

when the bytes cross a word boundary. SWR stores the right part of the register into the

appropriate part of the low-order word in memory; SWL stores the left part of the register into the

appropriate part of the high-order word in memory.

This instruction generates a 32-bit effective address that can point to any byte by sign-extending the

16-bit offset and adding it to the contents of general-purpose register base. Only the one word in

memory containing the designated starting byte is modified. Depending on the starting byte, from

one to four bytes are stored.

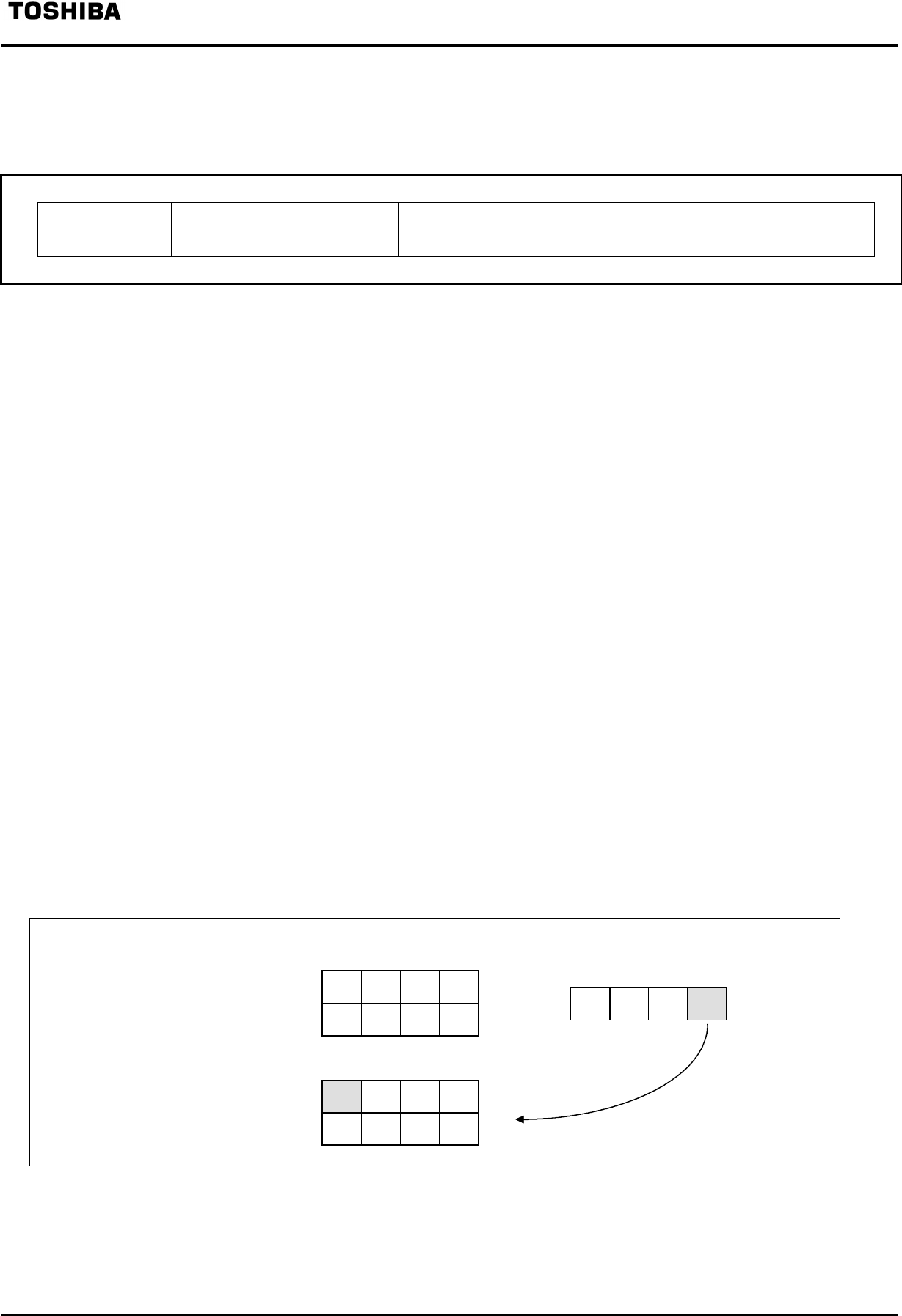

The concept is illustrated below. This instruction (SWR) starts from the low-order (right-most)

byte of the register and stores it into the designated memory byte; it then continues storing bytes

from register to memory, proceeding toward the high-order byte of the register and the high-order

byte of the memory word, until it reaches the high-order byte of the memory word.

No Address Error instruction is raised due to misalignment.

Memory

(Big endian)

Before

storing

SWR $24,4($0)

After

storing

Address 4 D 5 6 7

Address 0 0 1 2 3

Address 4 4 5 6 7

Address 0 0 1 2 3

Register

A B C D $24