Architecture

123

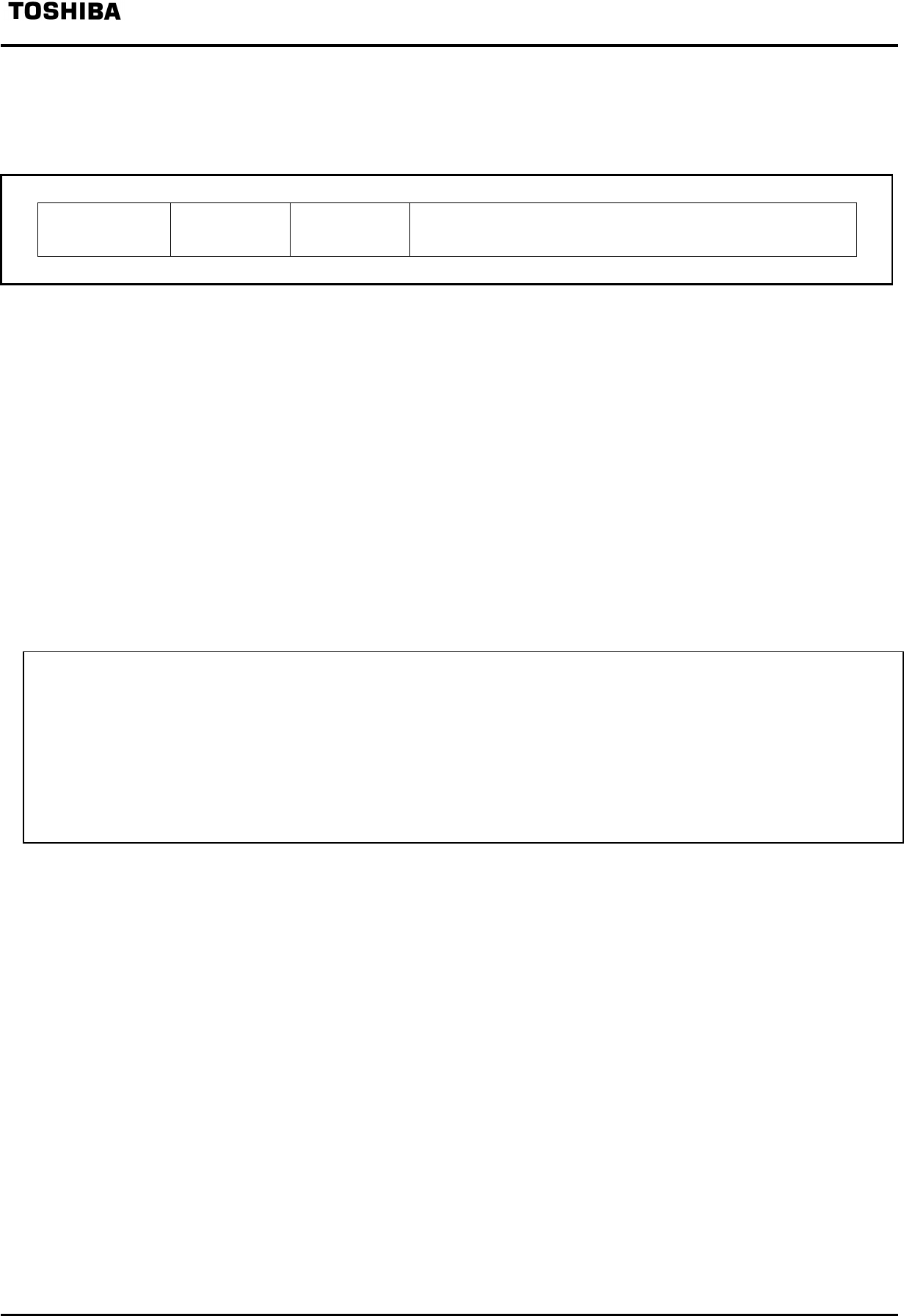

BGTZL Branch On Greater Than Zero Likely BGTZL

31 26 25 21 20 16 15 0

BGTZL

010111

rs

0

00000

offset

6 5 5 16

Format :

BGTZL rs, offset

Description :

Generates a branch target address by adding the address of the instruction in the delay slot to the 16-

bit offset (that has been left-shifted two bits and sign-extended to 32 bits). If the value in general-

purpose register rs is positive (i.e., the sign bit of rs is 0 and the rs value is not 0), the program

branches to the target address after a one-cycle delay. If the branch is not taken, the instruction in

the delay slot is treated as a NOP.

Operation :

T:

T + 1:

target ← (offset

15

)

14

|| offset || 0

2

condition ← (GPR[rs]

31

= 0) and (GPR[rs] ≠ 0

32

)

if condition then

PC ← PC + target

else

NullifyCurrentInstruction

endif

Exceptions :

None