TMPR3901F

224

4.3 Write Operation

The TMPR3901F supports only single write operations for writes.

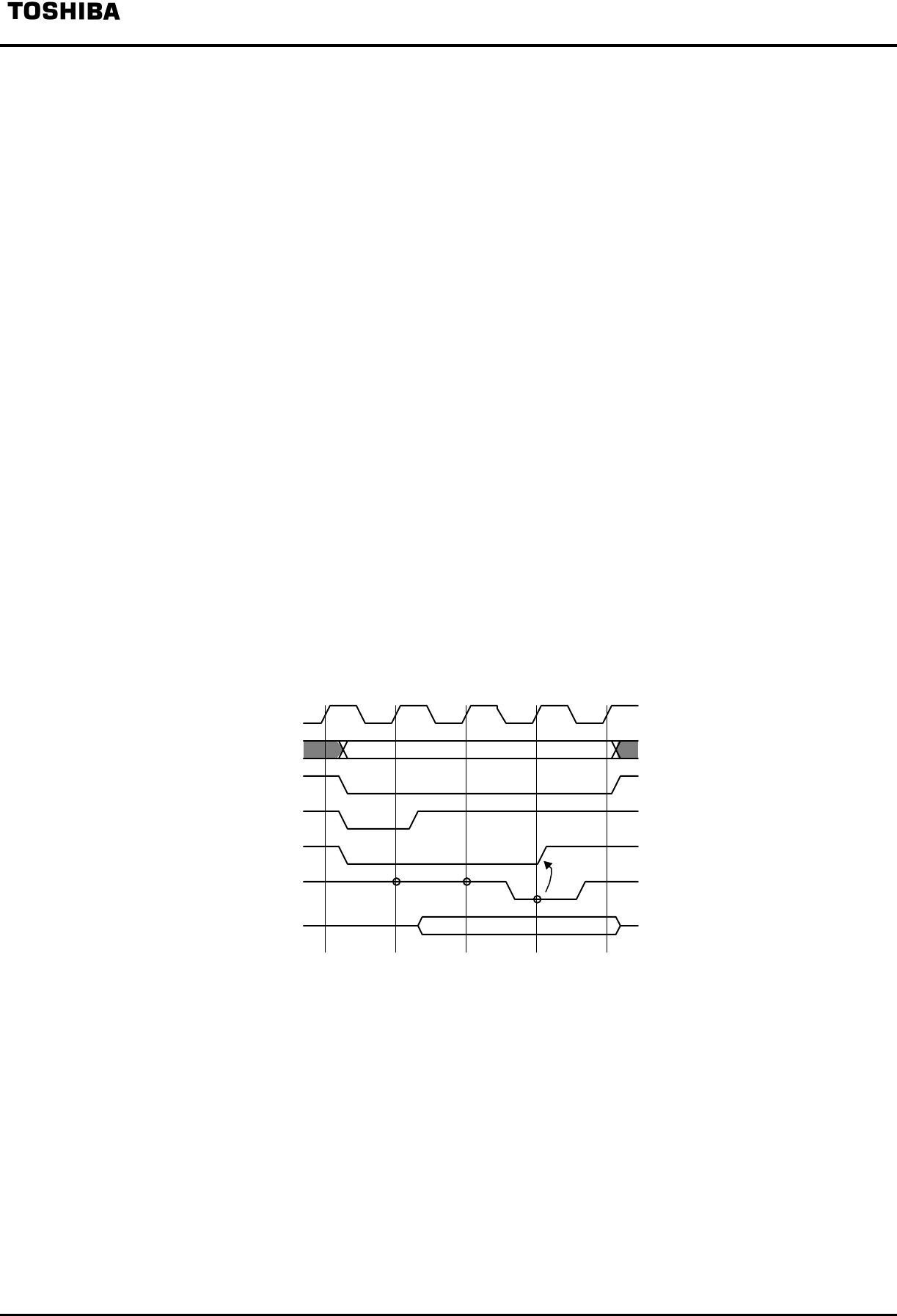

Figure 4-5 shows the timing for a single-write operation.

At the start of the operation, the BSTART* signal is asserted for one clock only. At the same time the WR*

and LAST* signals are asserted. Then the address A[31:2] and BE[3:0]* signals are valid.

Data is output to the data bus D[31:0] from the second clock after the start of the single-write cycle. An

external circuit latches the data and asserts an ACK* signal.

The TMPR3901F confirms the ACK* signal and on the next clock ends the single-write cycle.

The LAST* signal is deserted in the same clock cycle in which ACK* assertion is confirmed. The WR*

signal is asserted up until the single write cycle ends. The BE[3:0]*, A[31:2], and D[31:0] signals remain

valid until the end of the single write cycle.

The TMPR3901F ignores BUSERR* during a single write cycle. A single write cycle can therefore be ended

with an ACK* signal alone. Notifying the R3900 Processor Core of trouble requires asserting an interrupt

signal.

Figure 4-5 Single write operation (2 waits)

SYSCLK

A[31:2]

BE[3:0]*

WR*

BSTART*

LAST*

ACK*

D[31:0]