Architecture

64

6.3 Exception Details

6.3.1 Memory location of exception vectors

Exception vector addresses are stored in an area of kseg0 or kseg1.

The vector address of the Reset and NmI exceptions is always in a non-cacheable area of kseg1.

Vector addresses of the other exceptions depend on the Status register BEV bit. When BEV is 0 the

other exceptions are vectored to a cacheable area of kseg0.

When BEV is 1, all vector addresses are in a non-cacheable area of kseg1.

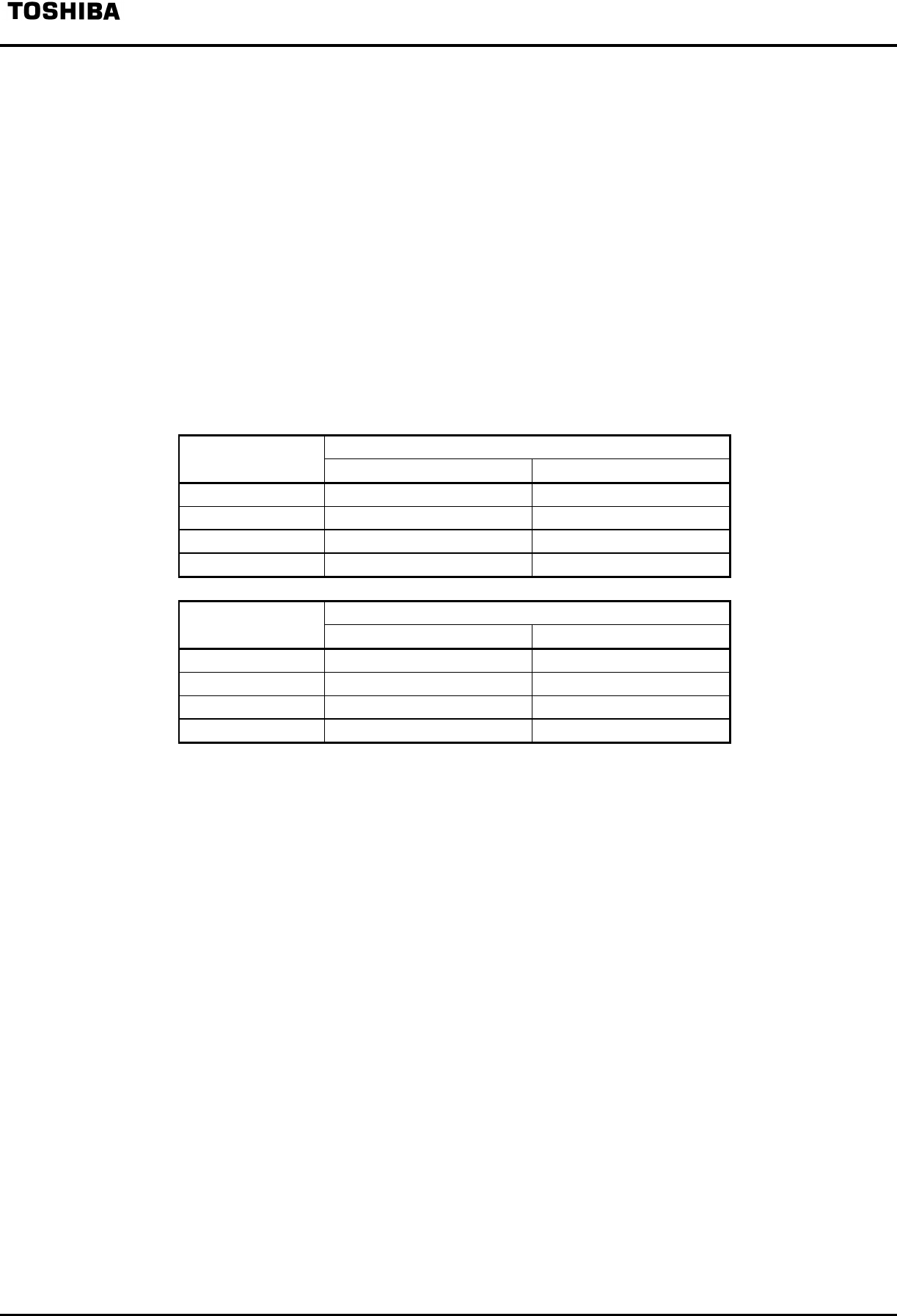

Exception Vector address (virtual address)

BEV bit = 0 BEV bit = 1

Reset, NmI 0xBFC0 0000 0xBFC0 0000

UTLB Refill 0x8000 0000 0xBFC0 0100

Debug 0xBFC0 0200 0xBFC0 0200

Other 0x8000 0080 0xBFC0 0180

Exception Vector address (physical address)

BEV bit = 0 BEV bit = 1

Reset, NmI 0x1FC0 0000 0x1FC0 0000

UTLB Refill 0x0000 0000 0x1FC0 0100

Debug 0x1FC0 0200 0x1FC0 0200

Other 0x0000 0080 0x1FC0 0180

The virtual address 0xBFC0 0200 is used as the vector address for Debug exceptions. Details are

given in Chapter 8.