Architecture

53

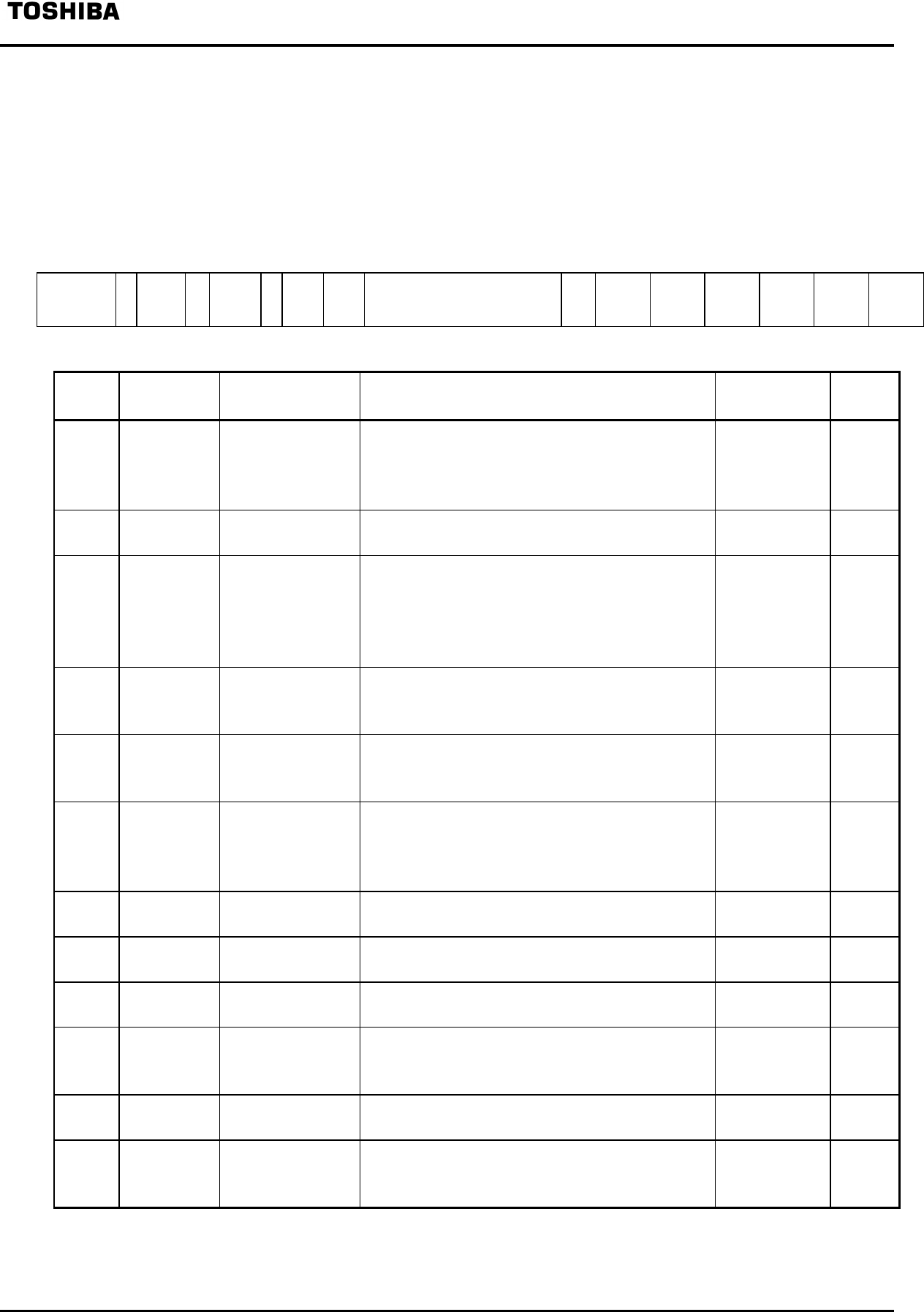

6.2.3 Status register (register no.12)

This register holds the operating mode status (user mode or kernel mode), interrupt masking status,

diagnosis status and similar information.

31 28 25 22 21 20 19 16 15 8 76 5 4 3 2 1 0

CU[3:0] 0 RE 0 BEV T

S

Nml 0 IntMask

Int[5:0] Sw[1:0]

0 KUo IEo KUp IEp KUc IEc

4 2 1 2 1 1 1 4 8 2 1 1 1 1 1 1

Bits Mnemonic Field name Description

Value on

Reset

Read/

Write

31-28 CU Coprocessor

Usability

The usability of the four coprocessors

CP0 through CP3 is controlled by bits

CU0 to CU3, with 1 = usable and 0 =

unusable.

Undefined Read/

Write

25 RE Reverse

Endian

Setting this bit in user mode reverses the

initial setting of the endian.

Undefined Read/

Write

22 BEV

†

Bootstrap

Exception

Vector

When this bit is set to 1, if a UTLB Refill

exception or general exception occurs,

the alternate bootstrap vector (the vector

address shown in parentheses in Table

6-2) is used.

1 Read/

Write

21 TS

†

TLB Shutdown This bit is set to 1 when the TLB

becomes unusable. It is always set to 1

when the internal MMU is enabled.

1 Read

20 NmI Non-maskable

Interrupt

This bit is set to 1 when a non-maskable

interrupt occurs. Writing 1 to this bit

clears it to 0.

0 Read/

Write

15-8 IntMask Interrupt Mask These are mask bits corresponding to

hardware interrupts Int5..0 and software

interrupts Sw1..0. Here 1 = interrupt

enabled and 0 = interrupt masked.

Undefined Read/

Write

5 KUo Kernel/User

Mode old

0 = kernel mode;

1 = user mode.

Undefined Read/

Write

4 IEo Interrupt

Enabled old

1 = interrupt enabled;

0 = interrupt masked.

Undefined Read/

Write

3 KUp Kernel/User

Mode previous

0 = kernel mode;

1 = user mode.

Undefined Read/

Write

2 IEp Interrupt

Enabled

previous

1 = interrupt enabled;

0 = interrupt masked.

Undefined Read/

Write

1 KUc Kernel/User

Mode current

0 = kernel mode;

1 = user mode.

0 Read/

Write

0 IEc Interrupt

Enabled

current

1 = interrupt enabled;

0 = interrupt masked.

0 Read/

Write

†

Used mainly for diagnosis and testing.