Architecture

10

Table 2-1 lists the CP0 registers built into the R3900 Processor Core. Some of these registers are reserved

for use by an external memory management unit.

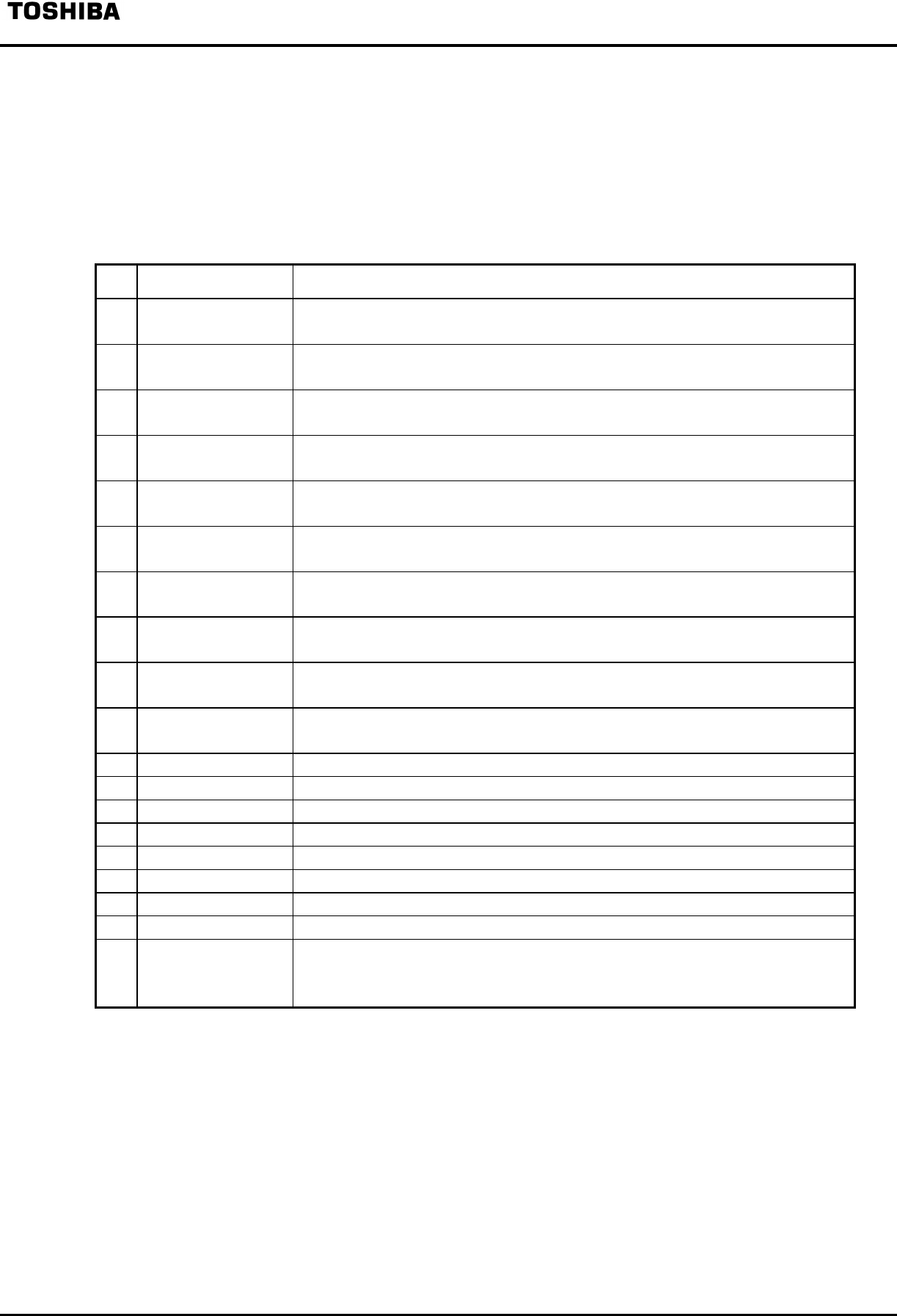

Table 2-1. List of system control coprocessor (CP0) registers

No Mnemonic Description

0

- (reserved)

†

1

- (reserved)

†

2

- (reserved)

†

3

Config

††

Hardware configuration

4

- (reserved)

†

5

- (reserved)

†

6

- (reserved)

†

7

Cache

††

Cache lock function

8

BadVAddr Last virtual address triggering error

9

- (reserved)

†

10 - (reserved)

†

11 - (reserved)

†

12 Status Information on mode, interrupt enabled, diagnostic status

13 Cause Indicates nature of last exception

14 EPC Exception program counter

15 PRId Processor revision ID

16 Debug

†††

Debug exception control

17 DEPC

†††

Program counter for debug exception

18

|

31

- (reserved)

†

†

Reserved for external memory management unit, when direct segment mapping

MMU is not used.

††

Additional R3900 Processor Core register not present in R3000A.

†††

Additional R3900 Processor Core Debug register not present in R3000A.