Architecture

25

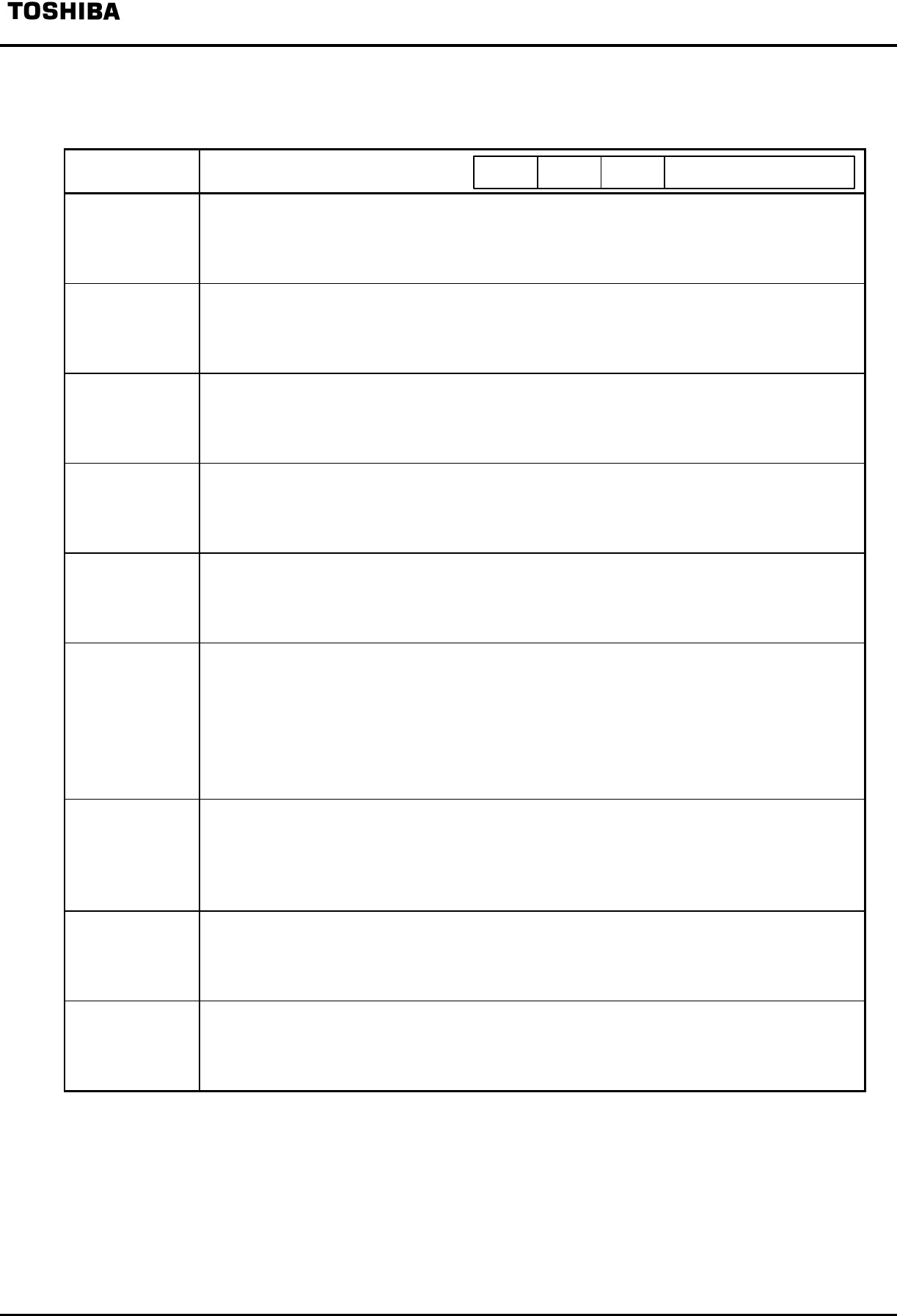

Table 3-2. Load/store instructions (1/2)

Instruction Format and Description

Load Byte LB rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Sign-extend the contents of the addressed byte and

load into register rt.

Load Byte

Unsigned

LBU rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Zero-extend the contents of the addressed byte

and load into register rt.

Load

Halfword

LH rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Sign-extend the contents of the addressed

halfword and load into register rt.

Load

Halfword

Unsigned

LHU rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Zero-extend the contents of the addressed

halfword and load into register rt.

Load Word LW rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Load the contents of the addressed word into

register rt.

Load Word

Left

LWL rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. This instruction is paired with LWR and used to

load word data not aligned with a word boundary. The LWL instruction loads

the left part of the word, and LWR loads the right part. LWL shifts the

addressed byte to the left, so that it will form the left side of the word, merges

it with the contents of register rt and loads the result into rt.

Load Word

Right

LWR rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. LWR shifts the addressed byte to the right, so that

it will form the right side of the word, merges it with the contents of register rt

and loads the result into rt.

Store Byte SB rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Store the contents of the least significant byte of

register rt at the addressed byte.

Store

Halfword

SH rt, offset (base)

Generate the address by sign-extending a 32-bit offset and adding it to the

contents of register base. Store the contents of the least significant halfword

of register rt at the addressed byte.

offsetrtbaseop