Architecture

137

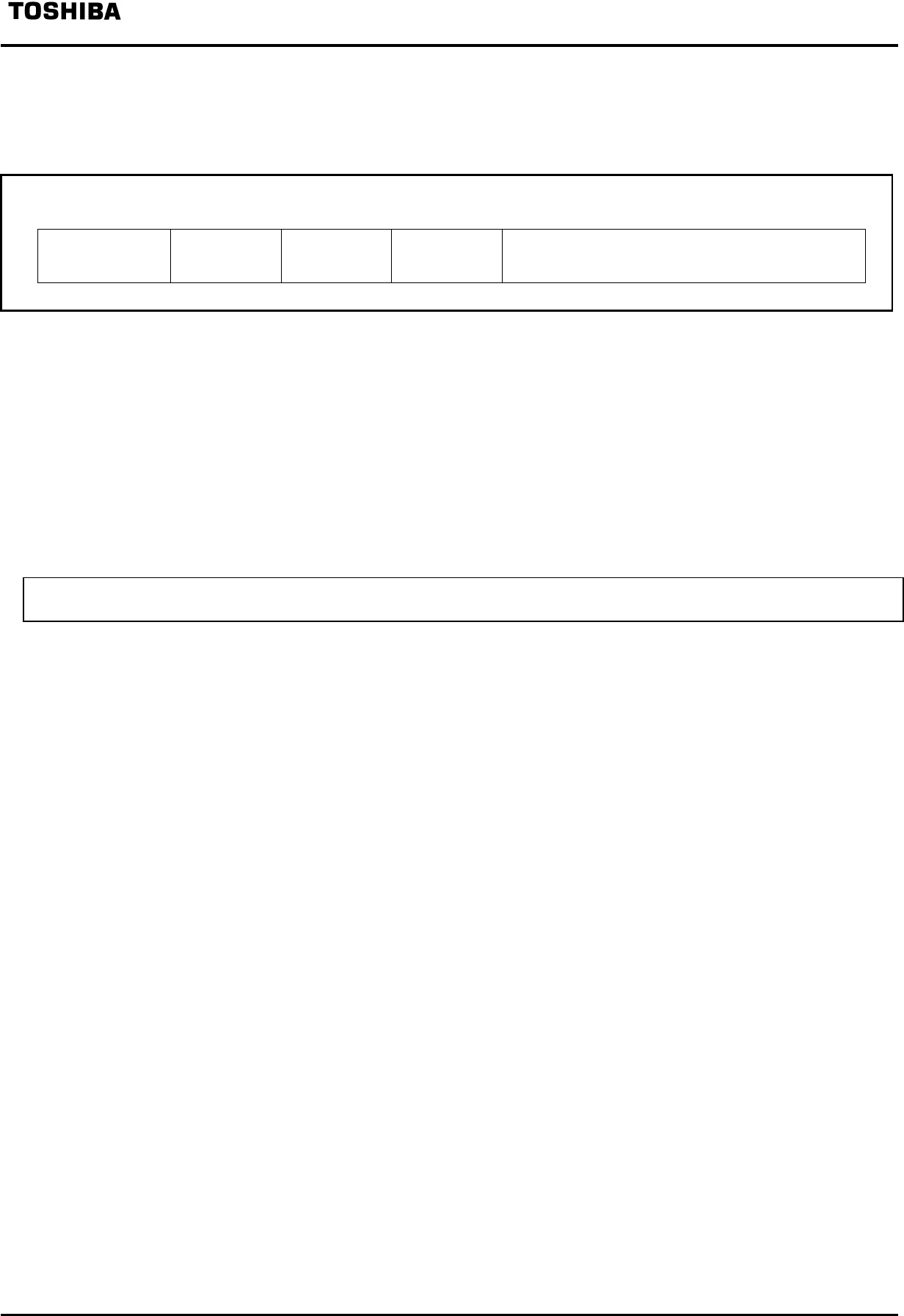

CTCz Move Control To Coprocessor CTCz

31 26 25 21 20 16 15 11 10

0

COPz

0100xx*

CT

00110

rt rd

0

000 0000 0000

6 5 5 5 11

Format :

CTCz rt, rd

Description :

Loads the contents of general register rt into control register rd of coprocessor z. This instruction is

not valid when issued for CP0.

Operation :

T:

CCR[z, rd] ← GPR[rt]

Exceptions :

Coprocessor Unusable exception

*Refer to the section entitied“Bit Encoding of CPU Instruction Opcodes”at the end of this appendix.