Instruction

Code

ACI

DATA

CE

data

ADC

REG

1000

lSSS

ADC

M

8E

ADD

REG

10000SSS

ADD

M

86

ADI

DATA

C6

data

ANA

REG

10100SSS

ANA

M

A6

ANI

DATA

E6

data

CALL

LABEL

CD

addr

CC

LABEL

DC

addr

CM

LABEL

FC

addr

CMA

2F

CMC

3F

CMP

REG

10111SSS

CMP

M

BE

CNC

LABEL

04

addr

CNZ

LABEL

C4

addr

CP

LABEL

F4

addr

CPE

LABEL

EC

addr

CPI

DATA

FE

data

CPO

LABEL

E4

addr

CZ

LABEL

CC

addr

DAA

27

DAD

RP

OORP

1001

OCR

REG

OOSS

S101

OCR

M

35

DCX

RP

OORP

1011

01

F3

EI

FB

HLT

76

IN

PORT

DB

data

INR

REG

OOSS

S100

INR

M

34

INX

RP

OORP

0011

JC

LABEL

DA

addr

JM

LABEL

FA

addr

JMP

LABEL

C3

addr

JNC

LABEL

02

addr

JNZ

LABEL

C2

addr

JP

LABEL

F2

addr

JPE

LABEL

EA

addr

JPO

LABEL

E2

addr

JZ

LABEL

CA

addr

LOA

ADDR

3A

addr

LDAX

RP

OOOX

1010

LHLD

ADDR

2A

addr

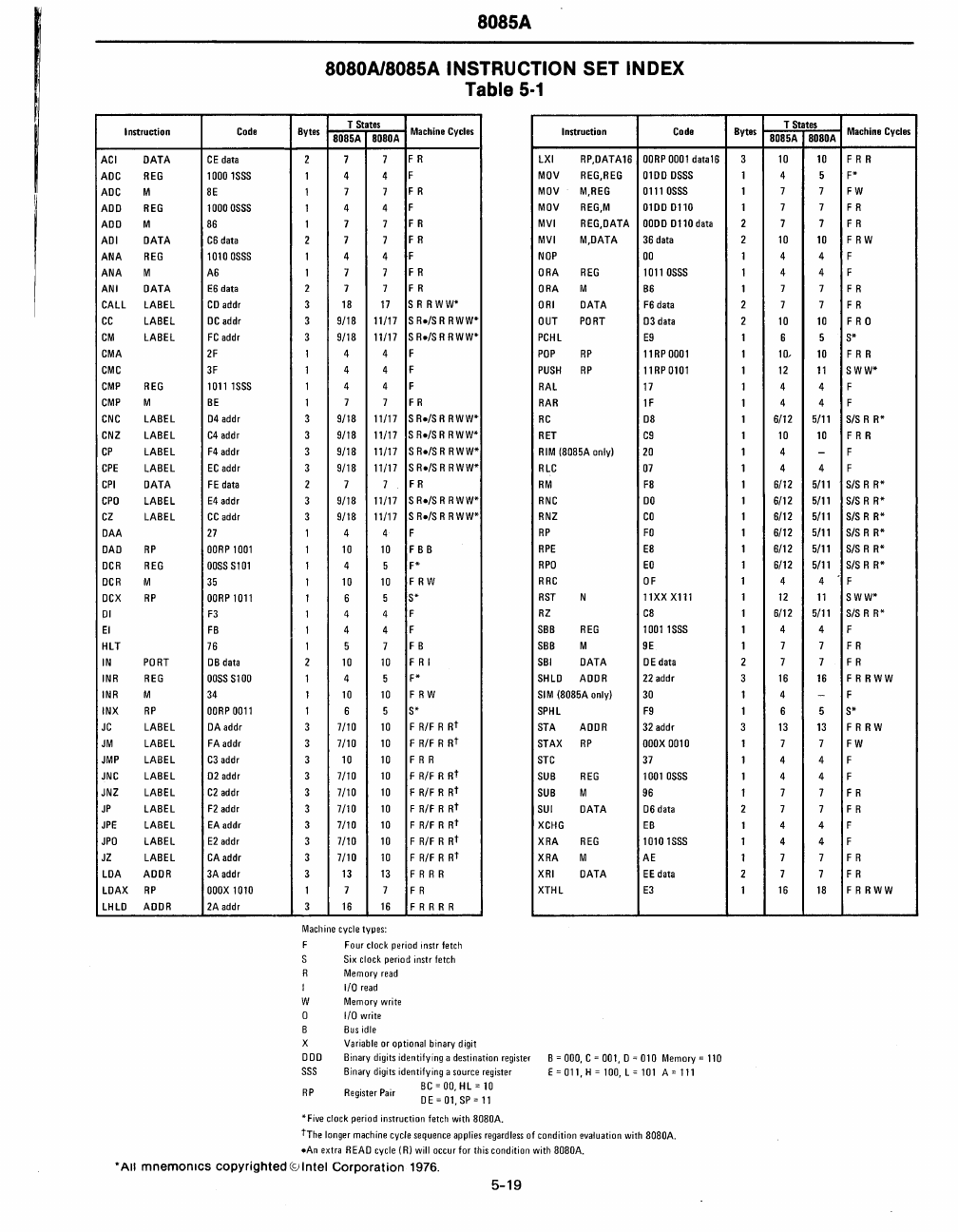

8085A

8080Al8085A INSTRUCTION SET INDEX

Table

5·1

Bytes

T

States

Machine

Cycles

BOB5A

BOBDA

2 7 7

F R

1 4 4

F

1

7 7

F R

1

4 4

F

1

7 7

F R

2

7

7

F R

1 4 4

F

1

7 7

F R

2 7 7

F R

3

18

17

SRRWW*

3

9/18

11/17

S R-/S R RWW*

3

9/18

11/17

SR_/SRRWW*

1 4 4

F

1

4 4

F

1

4 4 F

1

7 7 F R

3

9/18

11/17

SR-/SRRWW*

3

9/18

11/17

SR-/SRRWW*

3

9/18

11/17

SR_/SRRWW*

3

9/18

11/17

SR-/SRRWW*

2 7 7

FR

3

9/18

11/17

S R-/S R RWW*

3

9/18

11/17

SR_/SRRWW*

1 4 4 F

1

10 10

FBB

1 4 5 F*

1

10

10

F R W

1 6

5

S*

1 4 4

F

1 4 4

F

1 5 7

F B

2

10 10

F R I

1

4

5

F*

1

10 10

F R W

1

6 5

S*

3

7/10

10

F

R/F

R Rt

3

7/10

10

F

R/F

R Rt

3

10

10

F R R

3

7/10

10

F

R/F

R Rt

3

7/10

10

F

R/F

R Rt

3

7/10

10

F

R/F

R Rt

3

7/10

10

F

R/F

R Rt

3

7/10

10

F

R/F

R Rt

3

7/10

10

F

R/F

R Rt

3

13 13

F R R R

1

7

7

F R

3

16

16

F R R R R

Mach

ine

cycle

types:

Four

clock

period

instr

fetch

Six

clock

period

instr

fetch

Memory

read

lID

read

W

Memory

write

lID

write

X

DOD

SSS

RP

Bus

idle

Variable

or

optional

binary

digit

Binary

digits

identifying a

destination

register

Binary

digits

identifying a

source

register

Register

Pair

BC~00,HL~10

DE~OI,SP~11

*

Five

clock

period

instruction

fetch

with

aOaOA.

Instruction

Code

LXI

RP,DATA16

OORP

0001

data16

MOV

REG,REG

0100

DSSS

MOV

M,REG

01110SSS

MOV

REG,M

01000110

MVI

REG,DATA

00000110

data

MVI

M,DATA

36

data

NOP

00

ORA

REG

10110SSS

ORA

M

B6

ORI

DATA

F6

data

OUT

PORT

03

data

PCHL

E9

POP

RP

llRPOOOl

PUSH

RP

llRP

0101

RAL

17

RAR

IF

RC

08

RET

C9

RIM

(8085A

only)

20

RLC

07

RM

F8

RNC

DO

RNZ

CO

RP

FO

RPE

E8

RPO

EO

RRC

OF

RST

N

llXX

XIII

RZ

C8

SBB

REG

10011SSS

SBB

M

9E

SBI

DATA

DE

data

SHLD

ADDR

22

addr

SIM

(8085A

only)

30

SPHL

F9

STA

ADDR

32

addr

STAX

RP

OOOX

0010

STC

37

SUB

REG

1001

OSSS

SUB

M

96

SUI

DATA

06

data

XCHG

EB

XRA

REG

1010

ISSS

XRA

M

AE

XRI

DATA

EE

data

XTHL

E3

B

~

000,

C

~

001,

D

~

010

Memory

~

110

E

~

OIl,

H

~

100,

L

~

101

A

~

111

tThe

longer

machine

cycle

sequence

applies

regardless

of

condition

evaluation

with

a080A.

_An

extra

READ

cycle

(R)

will

occur

for

this

condition with

a080A.

"All

mnemonics

copyrighted

<0lntel

Corporation

1976.

5-19

Bytes

T

States

Machine

Cycles

BOBSA

BOBDA

3

10

10

F R R

1 4 5 F*

1

7 7

FW

1

7 7 F R

2 7 7 F R

2

10 10

F R W

1 4 4 F

1 4 4

F

1

7

7

F R

2 7 7

F R

2

10

10

FRO

1

6

5

S*

1

10,

10

F R R

1

12

11

SWW*

1 4 4

F

1

4

4

F

1

6/12

5/11

SIS

R

R*

1

10 10

F R R

1 4

- F

1

4 4 F

1

6/12

5/11

SIS

R

R*

1

6/12

5/11

SIS

R

R*

1

6/12

5/11

SIS

R

R*

1

6/12

5/11

SIS

R

R*

1

6/12

5/11

SIS

R

R*

1

6/12

5/11

SIS

R

R*

1 4 4 F

1

12

11

SWW*

1

6/12

5/11

SIS

R

R*

1

4 4 F

1 7 7 F R

2 7 7 F R

3

16 16

F R RWW

1

4

-

F

1 6 5

S*

3

13 13

F R R W

1 7 7 FW

1 4 4 F

1 4 4 F

1 7 7 F R

2

7

7

F R

1

4 4

F

1 4 4 F

1

7

7

F R

2 7 7 F R

1

16

18

FRRWW