inter

8080A/8080A·1/8080A·2

8·BIT

N·CHANNEL MICROPROCESSOR

• TTL Drive Capability

• 2

lAS

( - 1 :1.3

lAs,

- 2:1.5

lAs)

Instruction

Cycle

• Powerful Problem Solving Instruction

Set

•

6 General Purpose Registers and an

Accumulator

•

16·Bit Program Counter for Directly

Addressing up to 64K Bytes of

Memory

• 16·Bit Stack Pointer and Stack

Manipulation Instructions

for Rapid

Switching of the Program Environment

• Decimal, Binary, and Double Precision

Arithmetic

• Ability to Provide Priority Vectored

Interrupts

•

512 Directly Addressed 1/0 Ports

• Available

in

EXPRESS

- Standard Temperature Range

The Intel® 8080A is a

complete

8-bit parallel central

processing

unit

(CPU). It is fabricated on a

single

LSI

chip

using

Intel's n-channel silicon gate MOS process. This

offers

th~

user

a high

performance

solution

to

control

and

processing

applications.

The 8080A

contains

6

8-bit

general

purpose

working

registers

and

an accumulator. The 6 general purpose registers may be

addressed

individually

or

in pairs

providing

both

single

and

double

precision

operators.

Arithmetic

and

logical

instructions

set

or

reset 4 testable flags. A

fifth

flag provides

decimal

arithmetic

operation.

The

8080A has an external

stack

feature wherein any porti'on

of

memory

may be used as a last

in/first

out

stack

to

store/retrieve

the

contents

of

the

accumulator, flags,

program

counter, and all

of

the

6 general purpose registers. The 16-bit

stack

pointer

controls

the

addressing

of

this external stack. This

stack

gives

the

8080A

the

ability

to

easily handle

multiple

level

priority

interrupts

by

rapidly

storing

and restoring

processor

status. It also provides almost

unlimited

subroutine

nesting.

This

microprocessor

has been designed

to

simplify

systems design. Separate 16-line address and a-line

bidirectional

data

busses are used

to

facilitate easy

interface

to

memory

and

I/O.

Signals

to

control

the

interface

to

memory

and I/O are

provided

directly

by

the

8080A. Ultimate

control

of

the

address and data busses resides

with

the

HOLD signal. It provides

the

ability

to

suspend

processor

operation

and force

the

address and data busses

into

a high impedance state. This

permits

OR-tying these busses

with

other

controlling

devices

for

(DMA)

direct

memory

access

or

multi-processor

operation.

NOTE:

The

8080A

is

functionally

and

electrically compatible with

the

Intel®

8080.

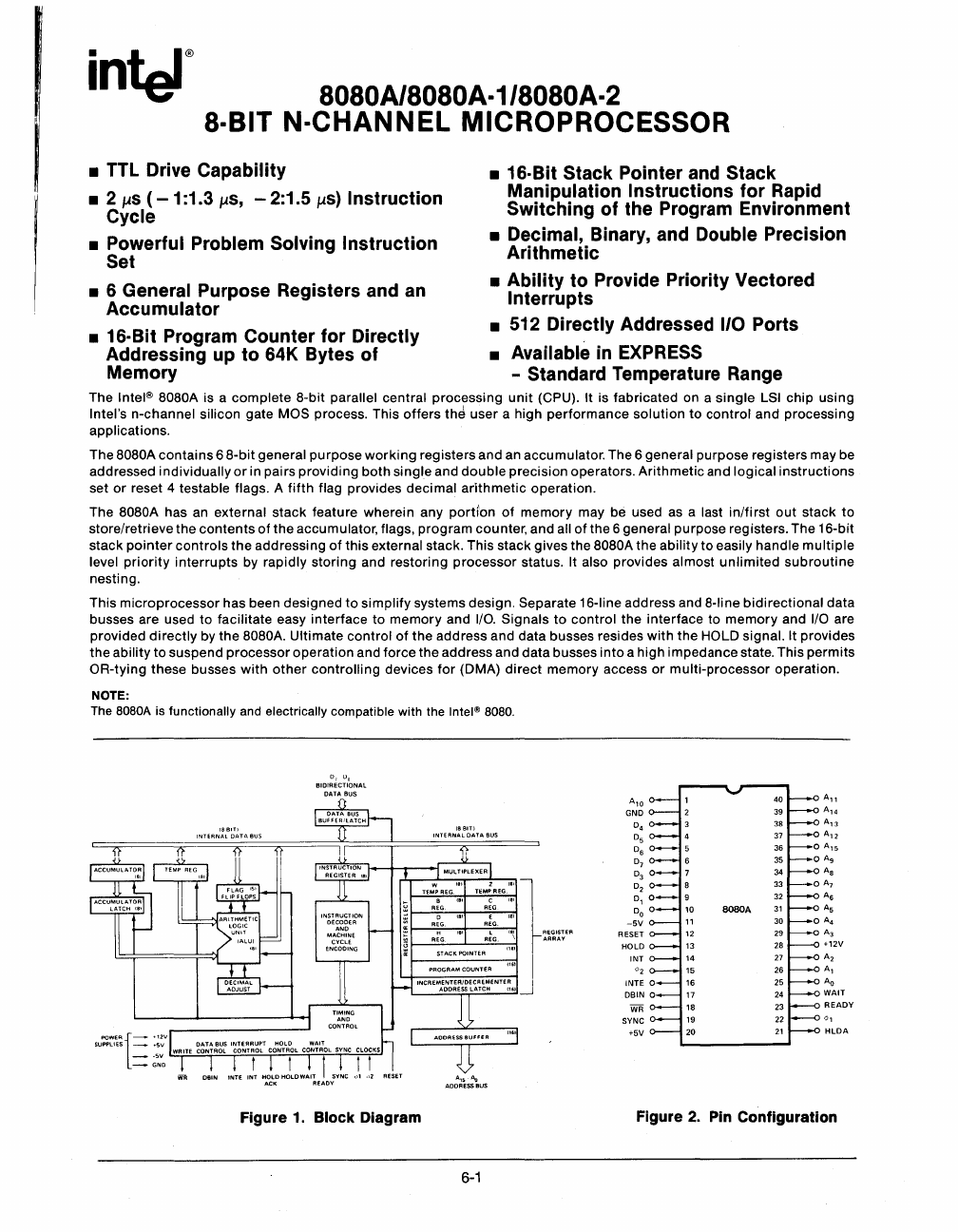

Figure

1.

Block Diagram

6-1

RESET

HOLD

INT

WR

SYNC

+5V

A3

+,2V

A2

A,

Ao

WAIT

READY

0,

HLDA

Figure

2.

Pin

Configuration