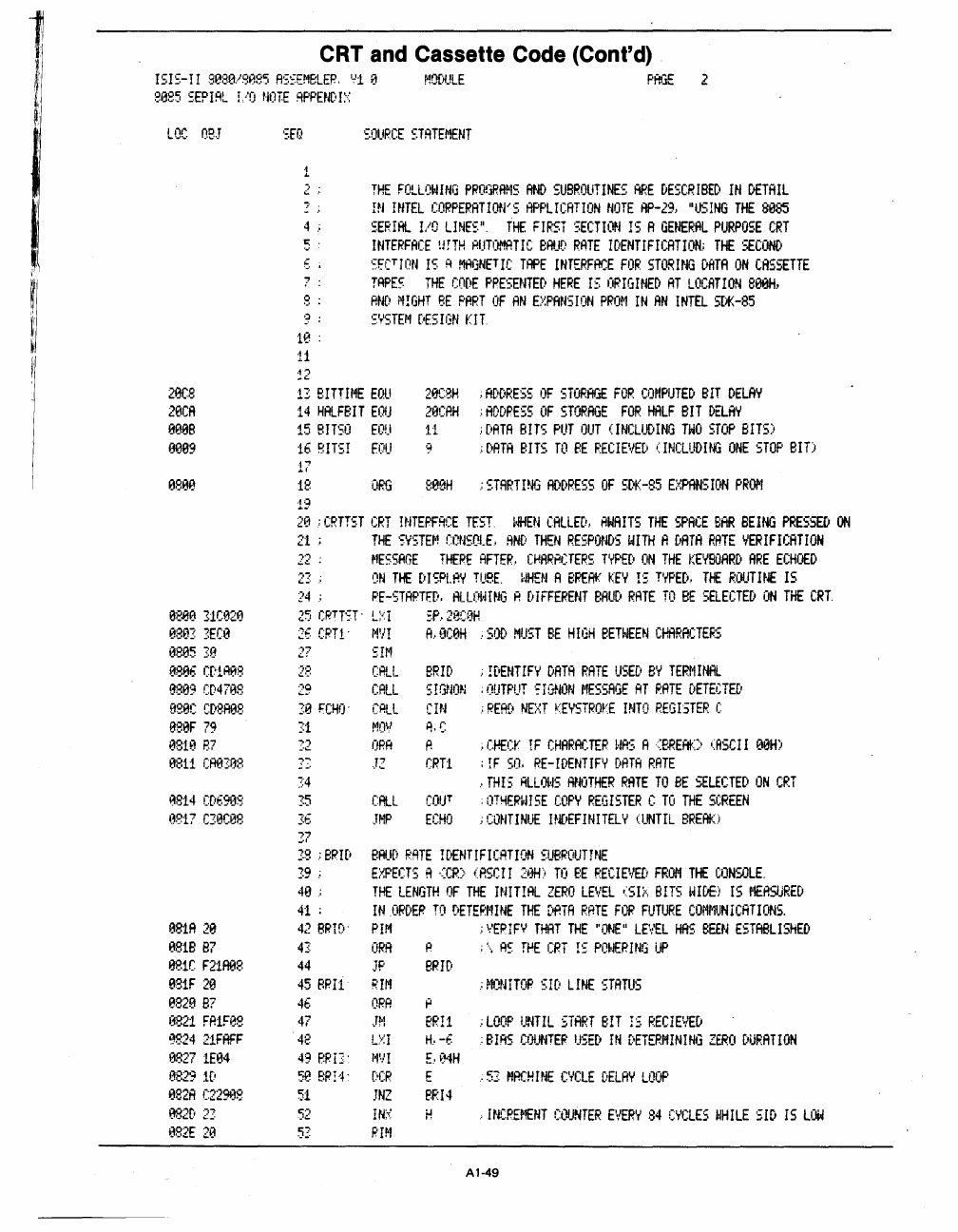

CRT and Cassette Code (Cont'd)

ISIS-II

80:313/8118'5

ASSEMBLER.

'"'1

0

:?e85

SEPIAL

i/O

1·10r.E

APPHIOI

>::

PAGE

2

lOC

08J

2OC8

2eCA

aOOB

0099

0see

02.013

11C0213

e80?

?Ece

aees

?B

08e6

CP1RI?t8

98139

W470S

98ac

weAes

B:?eF

79

13810

87

13814

C[l6908

13817

cace8

aS1A

29

e81B

87

ee1C

F21Ae8

galF

29

13829

B7

13821

FMF0S

~824

21FHF!='

13827

lE04

13829

1(,

eS2A

(:229138

eB2D

2?

i382E

2i3

SOIJRCE

STATEMHlT

1

2

.:

THE

FOLLO~~ING

P~O(JRA~lS

At-ID

SUBROUTINES

ARE

DESCRIBED

IN

DETAIL

:

..

'

IN

HITEL

CORPERATIOWS

APPLICATION

NOTE

AP-29,

"USING

THE

a0S5

4

.:

SERlf'tI..

I/O

LINES".

THE

FIF.:Si

SECTION

IS

A

GENERIiL

PURPOSE

CRT

5 .

INTERFACE

tHTH

~UTt)MATIC

BAt!!)

RATE

WENTIFICATION.:

THE

~.ECOND

S .

~J:TTWN

IS

H

MAGNETIC

TAPE

INTERFACE

FOR

STORING

OftTA

ON

CASSETTE

? :

TAPES

THE

CODE

PRESENTED

HERE

IS

ORIGINED

AT

LOCATION

BOOH,

8 :

fmC!

MIGHT

8E

PART

OF

AN

E::-~PANSION

PP.O~l

IN

AN

INTEL

SDK-85

9 :

S'.'ST£M

(:f.S

IGN

n T

1~~

:

11

12

E

BITTIt1E

Eo.lI

20C8H

:

Af'ORESS

OF

SiORAfJE

FOR

COP1PUTEv

B

IT

DELAY

14

HAlFB

IT

EQlJ

23CAH

:

ADDRESS

OF

STORAl3E

FOR

HALF

BIT

DELAY

15

8ITSO

EO!J

11

....

.:

['ATA

BITS

POT

OI.lT

(INCLUDING

TWO

STOP

BITS)

16

8ITS!

EI)U

9

.:

DATA

BITS

TO

BE

RECIEVE['

(INCLUDING

ONE

STOP

BID

17

18

ORG

~:eeH

.:

STARTING

AODRESS

OF

SCoK-S5

E:~PANSION

PROI'l

19

213

.:

eRTTST

CPT

HITEPFACE

TEST.

lHN

CALLED,

AWAITS

THE

SPACE

BAR

BEING

PRESSED

ON

21;

THE

';'r'STEt'l

CONSOLE

..

AND

THtN

RESPONDS

WITH

Po

[,ATA

R~TE

YERIFICATION

22

:

~1ESSAGE

THERE

AFTER.

CHARt=!CTERS

T'tPE(!

ON

THE

KE'''SOARD

ARE

ECHOED

21;

O~~

THE

£:tISPLP.Y

TUBE.

~iHEN

A

BREFW

KE'"

IS

WPED,

THE

I':OIJTHlE

15

24:

Pf-STAPTED.

AlLC~mlG

A

DIFFERENT

BAtiE)

RATE

TO

BE

SELECTED

ON

THE

CRT.

2~

CRTT'::r·

Ln

SP

..

28C:)H

26

CPT!'

Wi!

fl.OC€tH

.:

50(:0

MtlST

BE

HIGH

BETWEal

CHARACTERS

27

SIt1

2:::

CALL

BRIO

.;

WENTIF'r'

DATA

RATE

USED

B'"

TERtlIHAL

29

CALL

SrGNO~l

;

OUTPUT

':IG~ION

MESSAGE

AT

RATE

OETEGTEL'

:a

1=CI10'

CALI..

CHi:

REAr)

NE:':T

k:EYSTRorE

INTO

REGISTER

C

?-1

~101/

8.

~:

:2

ORA

A

.~

CHEer.

IF

CHARAI::TER

~lAS

A

<:BREAIC'

(ASCI

I

OOH)

(RH :

rF

50.

RE-IDENTIF't'

DATA

RATE

..

TH

I 5

ALUJl.1S

~~jTHER

RATE

TO

BE

SELECTED

ON

CRT

CALL

COUT

;

OT4ERmSE

COpy

REGISTER

C

TO

THE

SCREEN

36

~7

.IMP

ECHO

.:

CO~ITINUE

IN[IEFINITEL'r'

(UNTIL

8REAIO

?-8.:BPW

BAfJ[i

RATE

Ir.tEHTIFICATION

SUBROUTTNE

1.9

;

413;

41

;

E:~PECTS

A

'::CR)

(Poser

r

2i3l{:,

TO

E:E

PECIEVEfi

FRO/'!

THE

CONSOLE.

THE

LENGTH

(f

THE

WITIAL

ZERO

LEVEL

'.:51i<,

BITS

tHDE)

IS

~1EP'SIjREO

IN

.ORDER

TI)

[lETEP~1INE

THE

DATA

RRTE

FOR

FUTURE

COMt1IJNICATIONS.

42

BRIO'

PIt1

.:

VEPIFY

THAT

THE

"Ot-lE"

LEVEL

HAS

E'.EEN

ESTflBLISHED

ORA

44

jp

45

PoPIi

RIM

46

ORA

47

J1'!

·48

U':I

49

BP.E.:

11vr

:.e

ep!

'l

. [:{R

51

JNZ

52

w;':

51

RIM

P-

BRm

fi

: \

AS

THE

CRT

I S

PO~lER

LNG

UP

.;

~~JN

nOR

5 W L

HIE

STATlIS

eR!1

.;

LOOP

UNTIL

STA~:T

BIT

15

RECIE'·/ED

H

..

-6:

BIAS

COUNTER

USED

IN

[:t£TERtofINING

ZERO

[JURATION

E.

tt.iH

E

.:

51

MRCHINE

C'r'CLE

DELAY

LOOP

8RI4

H,

m::RHlENT

COUNTER

EVER"

84

C'r'CLE5

WHILE

SID

IS

l!lol

A1-49