THE INSTRUCTION SET

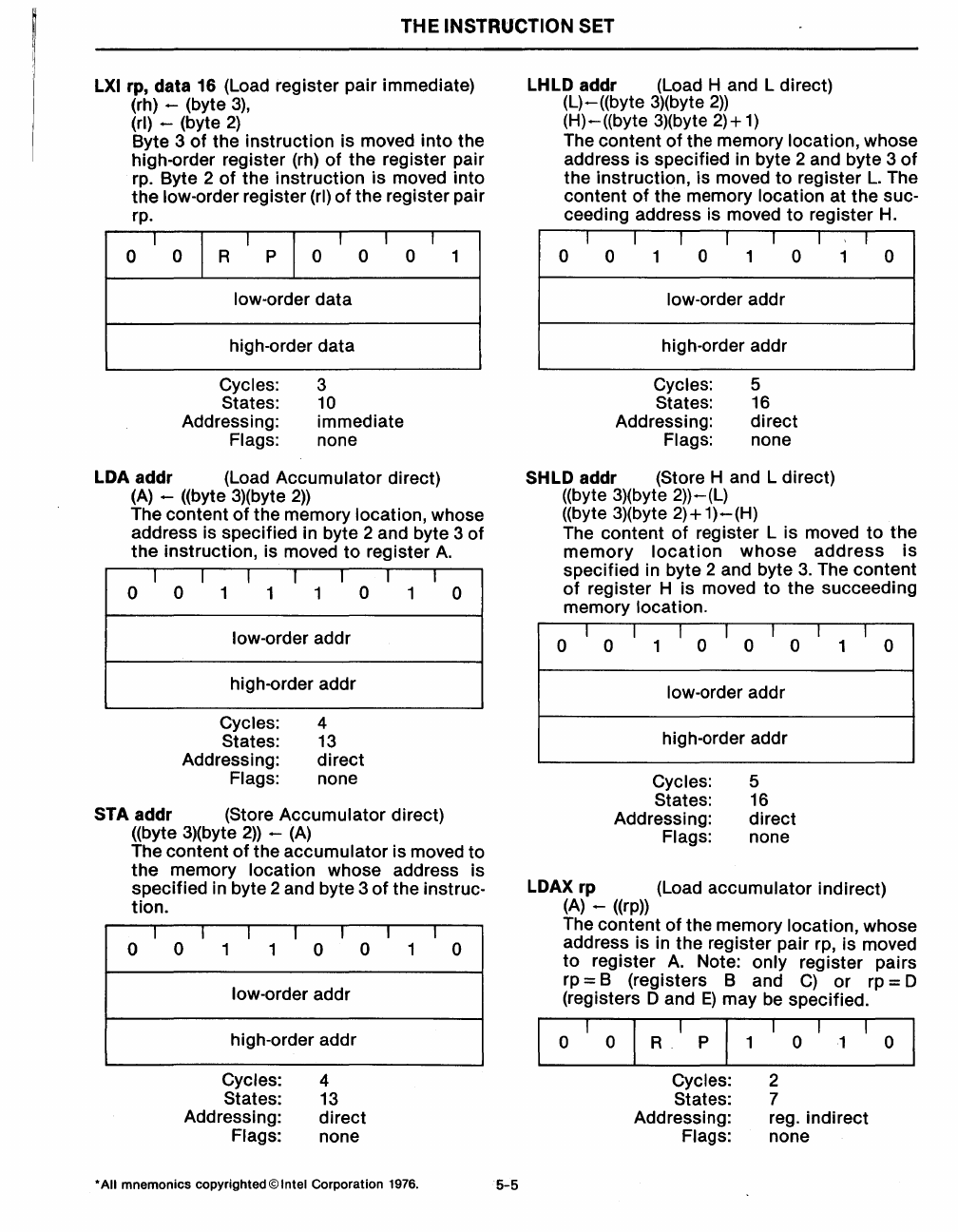

LXI rp, data 16 (Load register

pair

immediate)

(rh) - (byte

3),

(rl) - (byte

2)

Byte 3

of

the

instruction

is moved

into

the

high-order register (rh)

of

the

register pair

rp. Byte 2

of

the

instruction

is

moved

into

the

low-order register (rl)

of

the

register pair

rp.

o I 0 I

I I I

I

R P 0 0

low-order

data

high-order

data

Cycles:

3

States:

Addressing:

10

immediate

none Flags:

I

0

LDA addr (Load

Accumulator

direct)

(A)

- ((byte 3)(byte 2»

1

The

content

of

the

memory location, whose

address is specified in byte 2 and byte 3

of

the

instruction,

is moved

to

register

A.

I

0

I I

, 1

I

0 1

1

0

low-order addr

high-order addr

Cycles: 4

States:

Addressing:

13

direct

none

Flags:

I I

1

STA addr

(Store

Accumulator

direct)

((byte 3)(byte 2» -

(A)

0

The

content

of

the

accumulator

is moved

to

the

memory

location

whose address is

specified

in byte 2 and byte 3

of

the instruc-

tion.

I

0

0

I

I

1 ' 0

I

1

0

low-order addr

high-order addr

Cycles:

4

States:

Addressing:

13

direct

none

Flags:

I I

1

0

*AII mnemonics

copyrighted©lntel

Corporation

1976.

5-5

LHLD addr (Load

Hand

L direct)

(L)-((byte

3)(byte

2»

(H)-((byte

3)(byte

2)

+

1)

The

content

of

the memory

location,

whose

address

is

specified in byte 2 and byte 3

of

the

instruction,

is moved

to

register

L.

The

content

of

the

memory

location

at

the

suc-

ceeding address is moved

to

register H.

I

0

0

,

,

I

I

1

0 1

0

low-order addr

high-order addr

Cycles: 5

States:

Addressing:

16

direct

none Flags:

I

SHLD addr (Store

Hand

L direct)

((byte 3)(byte

2»-(L)

((byte 3)(byte

2)+

1)-(H)

' I

1 0

The

content

of

register L is moved

to

the

memory

location

whose

address

is

specified

in byte 2 and byte

3.

The

content

of

register H is moved

to

the

succeeding

memory location.

0

1

0

I

1

' 0 ' 0 I 0

low-order addr

high-order addr

Cycles: 5

States:

Addressing:

16

direct

none

Flags:

I

1

I 0

LDAX

rp

(Load

accumulator

indirect)

(A)

- ((rp»

The

content

of

the memory location,

whose

address is in

the

register pair rp,

is

moved

to

register

A.

Note:

only

register

pairs

rp = B (registers B and

C)

or

rp = 0

(registers 0 and

E)

may

be specified.

Cycles:

States:

Addressing:

Flags:

2

7

reg.

indirect

none