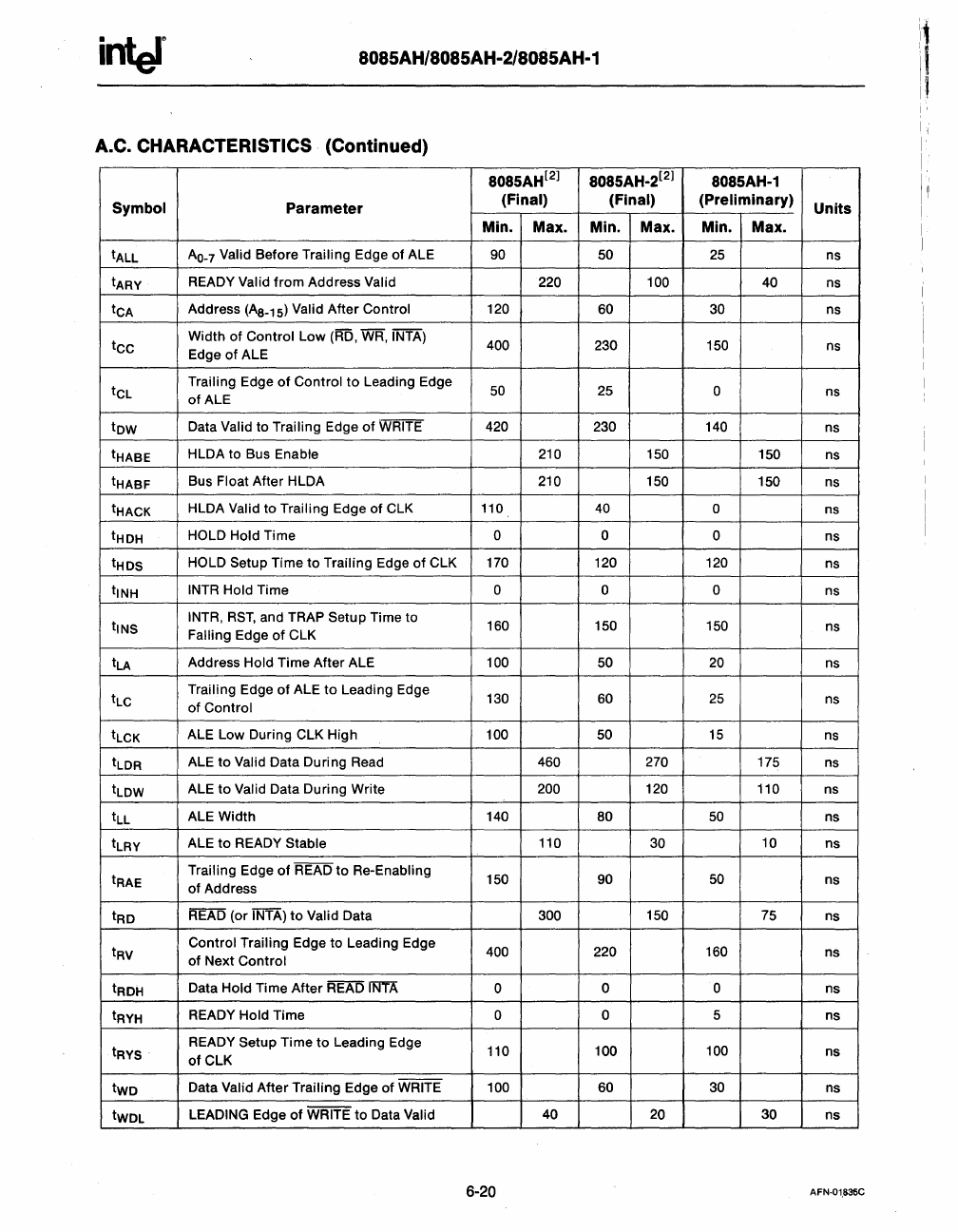

8085AH/8085AH-2/8085AH-1

A.C.

CHARACTERISTICS (Continued)

8085AH[2]

8085AH-2[2]

8085AH-1

Symbol

Parameter

(Final) (Final) (Preliminary)

Units

Min. Max. Min.

Max. Min.

Max.

tAll

AO-7

Valid Before Trailing Edge

of

ALE

90

50

25

ns

tARY

READY Valid

from

Address Valid

220

100 40

ns

tCA

Address (Aa-1S) Valid After Control

120

60

30 ns

tcc

Width

of

Control

low

(RD,

WR,

INTA)

400

230

150

ns

Edge

of

ALE

tCl

Trailing Edge

of

Control

to

leading

Edge

50

25

0

ns

of

ALE

tow

Data Valid to Trailing Edge

of

WRITE

420 230

140

ns

tHABE

HlDA

to Bus Enable

210

150

150

ns

tHABF

Bus

Float After

HlDA

210

150

150

ns

tHACK

HlDA

Valid to Trailing Edge

of

ClK

110

40

0

ns

tHOH

HOLD Hold Time

0 0 0

ns

tHOS

HOLD Setup Time

to

Trailing Edge

of

ClK

170

120

120

ns

tlNH

INTR Hold

Time

0 0 0

ns

tiNS

INTR,

RST,

and TRAP Setup Time to

160 150

150

ns

Falling Edge

of

ClK

tlA

Address Hold Time After ALE 100

50

20

ns

tlC

Trailing Edge

of

ALE

to

leading

Edge

130

60

25

ns

of

Control

tlCK

ALE

low

During

ClK

High

100

50

15

ns

tLOR

ALE

to

Valid Data During Read 460

270

175

ns

tlOW

ALE

to

Valid Data During Write

200

120

110

ns

tll

ALE Width

140 80

50

ns

tlRY

ALE

to

READY Stable 110

30

10

ns

tRAE

Trailing Edge

of

READ

to

Re-Enabling

150

90

50

ns

of

Address

tRO

READ (or INTA)

to

Valid Data 300

150

75

ns

tRV

Control Trailing Edge

to

leading

Edge

400 220

160

ns

of

Next Control

tROH

Data Hold Time After READ

lNTA

0

0 0

ns

tRYH

READY Hold Time

0 0 5 ns

tRYS

READY Setup Time

to

leading

Edge

110

100

100

ns

ofClK

two

Data Valid After Trailing Edge

of

WRITE 100

60

30

ns

tWOL

lEADING

Edge

of

WRITE

to

Data Valid

40

20

30 ns

6-20

AFN·01,835C