M,

Tn

Tn+1

Tn+2

Tn+

3

Tn+(;-1)

Tn+i

T,

T2

n

i\

n n h

rl

r1

n

"

----1L

r--IL

----1L

~

~

----1L

~----1L

RESET

INTERNAL

RESET

----1

'--'

~

--

- -

~~

"

"

t::

FLOATING

PC= 0

-

--

-

-\

UNKNOWN I

\

SYNC

I

~

DBIN

r-

STATUS

INFORMATION

"

"

X0

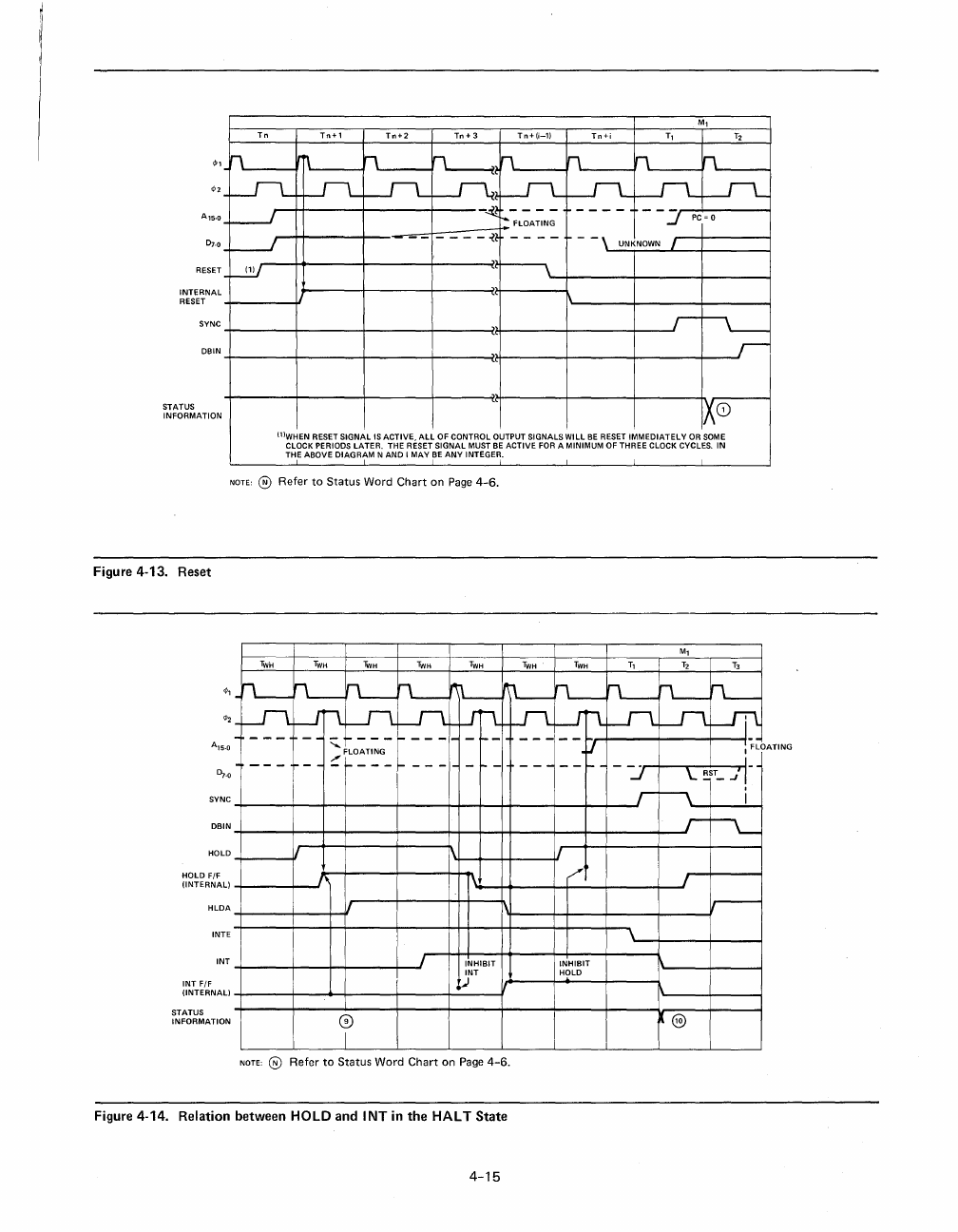

I1IWHEN RESET SIGNAL

IS

ACTIVE,

ALL

OF CONTROL OUTPUT SIGNALS

WILL

BE

RESET

IMMEDIATELY

OR

SOME

CLOCK PERIODS LATER. THE RESET SIGNAL MUST

BE

ACTIVE

FOR

A MINIMUM OF THREE CLOCK CYCLES.

IN

THE ABOVE

DIAGRAM

N AND I

MAY

BE

ANY

INTEGER.

NOTE:

® Refer

to

Status

Word

Chart

on Page

4-6,

Figure 4-13. Reset

Tw'H

TWH

TWH

TWH TWH

TWH

rL-

rL-

rL-

rL-

~

'\L-

L--

SYNC

DBIN

HOLD

HOLD

F/F

(INTERNAL)

HLDA

INTE

INT

INT

F/F

(INTERNAL)

STATUS

INFORMATION

~

Wl

~

~

JrL

-

---

--

::::..~---

1----

-

r--

FLOATING

""

-

---

-

-~---

1----

-r-

II

,\

1\'

II

I

INHIBIT

INT

)

0

I

NOTE:

® Refer

to

Status

Word Chart on Page

4-6.

Figure 4-14. Relation between HOLD and INT

in

the

HALT State

4-15

W"l

---

M,

TWH

T,

T2

T3

rL-

rL-rL-

rL.-

Wn.

~

~4:

-

-.'1

I FLO

1-

_

--1--

~

!!ST_

J I

I

:---\ i

I

h-

1

,/

I

r-

\

INHIBIT

HOLD

K@

ATING