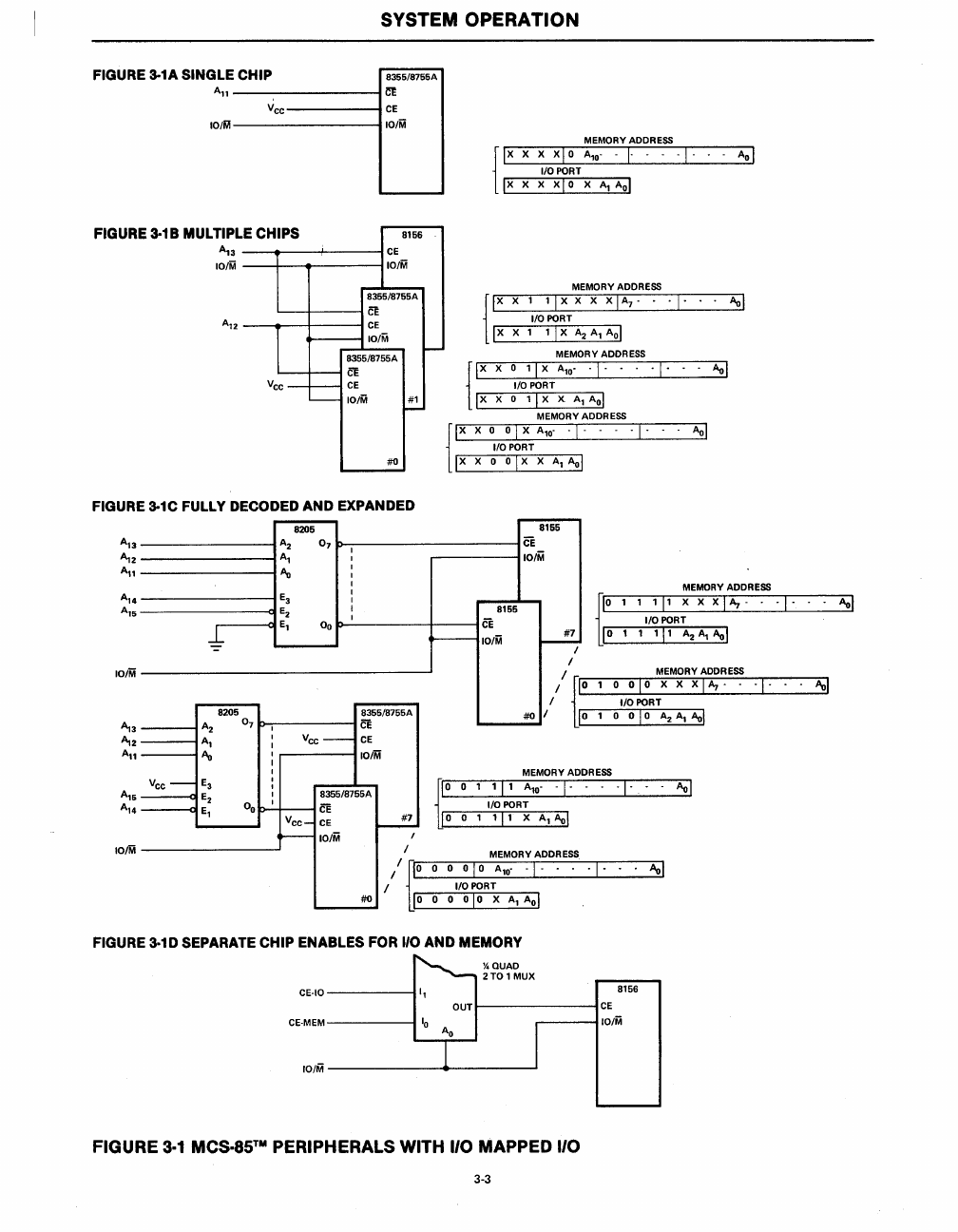

SYSTEM OPERATION

FIGURE 3-1A SINGLE

CHIP

8355/8755A

A"

_______

----1

~

vee----~CE

10/~-------__I10/M

FIGURE

3-1

B MULTIPL

ECHIPS

8156

A13

101M

Vee-

I---

'-----

CE

101M

8355/8755A

EE

CE

101M

8355/8755A

EE

CE

101M

#1

I-

#0

FIGURE 3-1C FULLY DECODED

AND

EXPANDED

8205

A'3

A,2

A2

07

I

A,

A'l

Ao

I--

MEMORY

ADDRESS

{

I X X X X I 0 A,o- -

1-

- I -

1/0

PORT

IX

X X X

lox

A,

Aol

MEMORY

ADDRESS

rX

x>

'I X X X X

I"·

. .

I·

1/0

PORT

IX

X 1 1 1 X

A2

A,

Aol

MEMORY ADDRESS

{

IX

X 0 1 1 X A,o- - 1 - - - - 1 -

1/0

PORT

IX

X 0 1 I X X

A,

Aol

MEMORY ADDRESS

t X ° ° 1

XA,,·

. 1 . . 1

1/0

PORT

IX

X 0 0 I X X

A,

Aol

8155

CE

101M

Aol

MEMORY

ADDRESS

A'4

A'5

101M

A,3

A,2

A11

A'5

A'4

101M

~

A

2

-----tAl

------lAo

vee

E3

----<lI

E

2

----<lIE,

8205

0

7

E3

E2

I

E,

00

8355/8755A

EE

CE

.------1

101M

8355/8755A

0

0

P-+-----I

EE

Vee

CE

#7

101M

I

8155

CE

~

101M

~

to

, ,

'I'

X X X I., . . 1 .

1/0

PORT

I

I

/~

#0 / 10

MEMORY

ADDRESS

olooloXXXI~-

-1-

MEMORY ADDRESS

ilo

PORT

fO",'A'11

I MEMORY ADDRESS

/

11~~IO~O~O~O~I~O~A=l~~~-~I-~~~-~I------~Ao~1

1/0

PORT

FIGURE 3·1D SEPARATE

CHIP

ENABLES FOR

1/0

AND

MEMORY

~

% QUAD

2TO

1 MUX

CE-IO

I,

8156

OUT

CE

10

101M

Ao

I

1

CE-MEM

101M

FIGURE

3·1

MCS·85™ PERIPHERALS WITH

110

MAPPED

110

3-3