FUNCTIONAL DESCRIPTION

2.3.6 HOLD and HALT States

The 8085A uses the T

HOLD

state

to

momentarily

cease executing machine cycles, allowing

ex-

ternal devices

to

gain control

of

the bus and

peform DMA cycles. The processor internally

latches the state

of

the HOLD line and the un-

masked interrupts during

ClK

=

"1"

of

every

T

HALT

state. If the internal latched HOLD signal

is high during

ClK

=

"1"

of any T

HALT

state, the

CPU

will

exit

T

HALT

and enter T

HOLD

on the

following

ClK

=

"1".

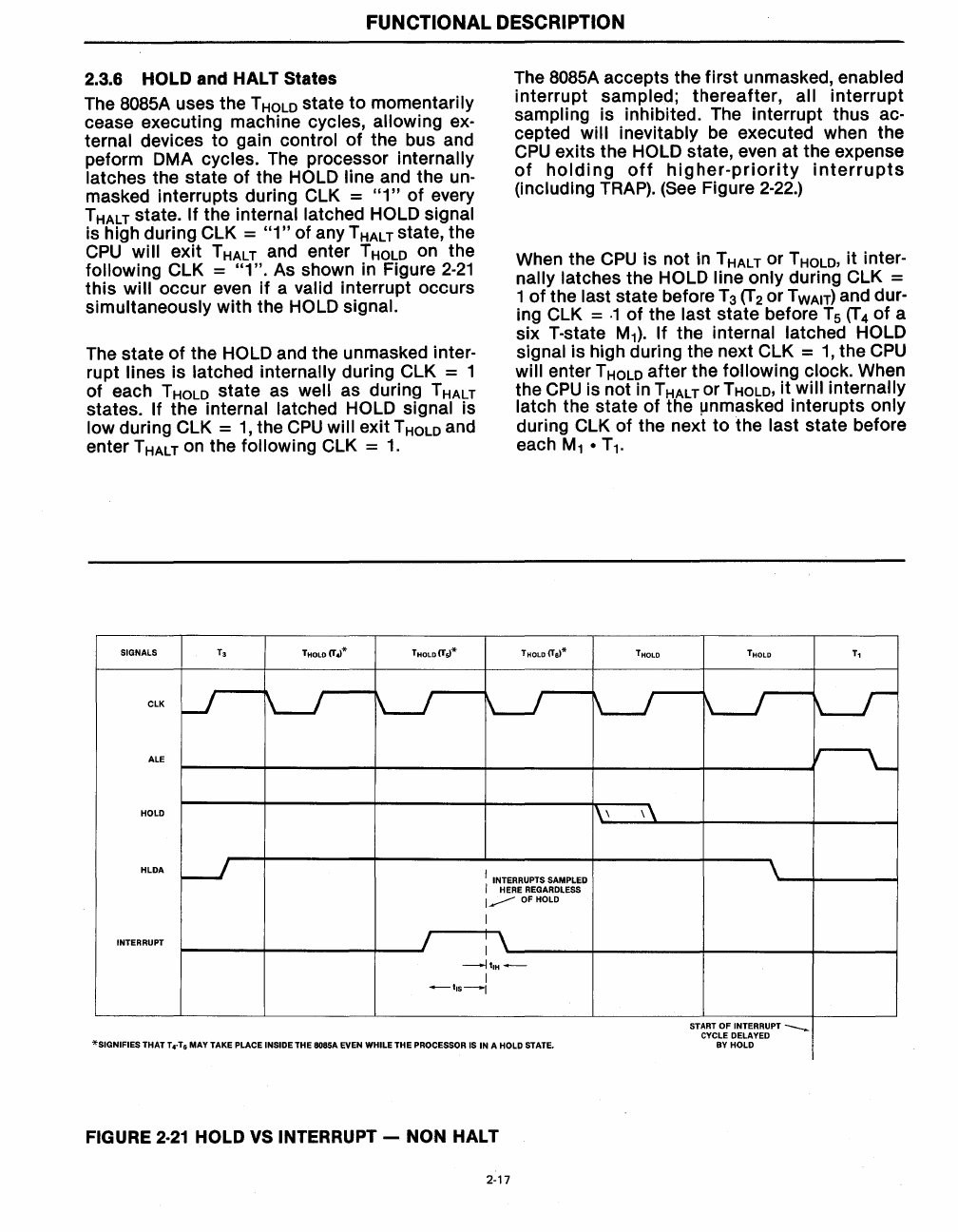

As shown in Figure

2-21

this

will

occur even

if

a valid interrupt occurs

simultaneously with the

HOLD signal.

The state

of

the HOLD and the unmasked inter-

rupt lines is latched internally during

ClK

= 1

of each T

HOLD

state as well as during T

HALT

states. If the internal latched HOLD signal is

low during

ClK

=

1,

the

CPU

will exit T

HOLD

and

enter T

HALT

on the following

ClK

=

1.

SIGNALS

To

THOLD

CT.>*

THOLDCTsI*

ClK

u-

'----1

ALE

HOLD

HLDA

~

INTERRUPT

The 8085A accepts the

first

unmasked, enabled

interrupt

sampled; thereafter, all

interrupt

sampling is inhibited. The interrupt thus ac-

cepted will inevitably be executed when the

CPU

exits the HOLD state, even at the expense

of

holding

off

higher-priority

interrupts

(including

TRAP).

(See

Figure

2-22.)

When the

CPU

is not

in

T

HALT

or T

HOLD,

it

inter-

nally latches the

HOLD line only during

ClK

=

1

of

the last state before T 3 (T 2 or T

WAIT)

and dur-

ing

ClK

=

·1

of

the last state before T 5 (T 4

of

a

six T-state

M1). If the internal latched HOLD

signal is high during the next

ClK

=

1,

the

CPU

will enter T

HOLD

after the following clock. When

the

CPU

is not in T

HALT

or

THOLD,

it

will internally

latch the state

of

the I-Inmasked interupts only

during

ClK

of

the next

to

the last state before

each

M1

• T

1

.

THOLD

CTa)*

T

HOLD

THOLD

T,

~

~

L-.r-

L-1

-

II

L

\\

\\

I INTERRUPTS SAMPLED

1 HERE REGARDLESS

1

__

OF HOLD

1

1\

1

--It'H-

1

--t,s-!

START

OF

INTERRUPT

___

CYCLE DELAYED

*SIGNIFIES

THAT

T.·T

a

MAY

TAKE PLACE INSIDE THE 8085A EVEN WHILE

THE

PROCESSOR

IS

IN A HOLD STATE. BY

HOLD

FIGURE

2·21

HOLD

VS

INTERRUPT - NON HALT

2-17