intJ

8085AH/8085AH-2/8085AH-1

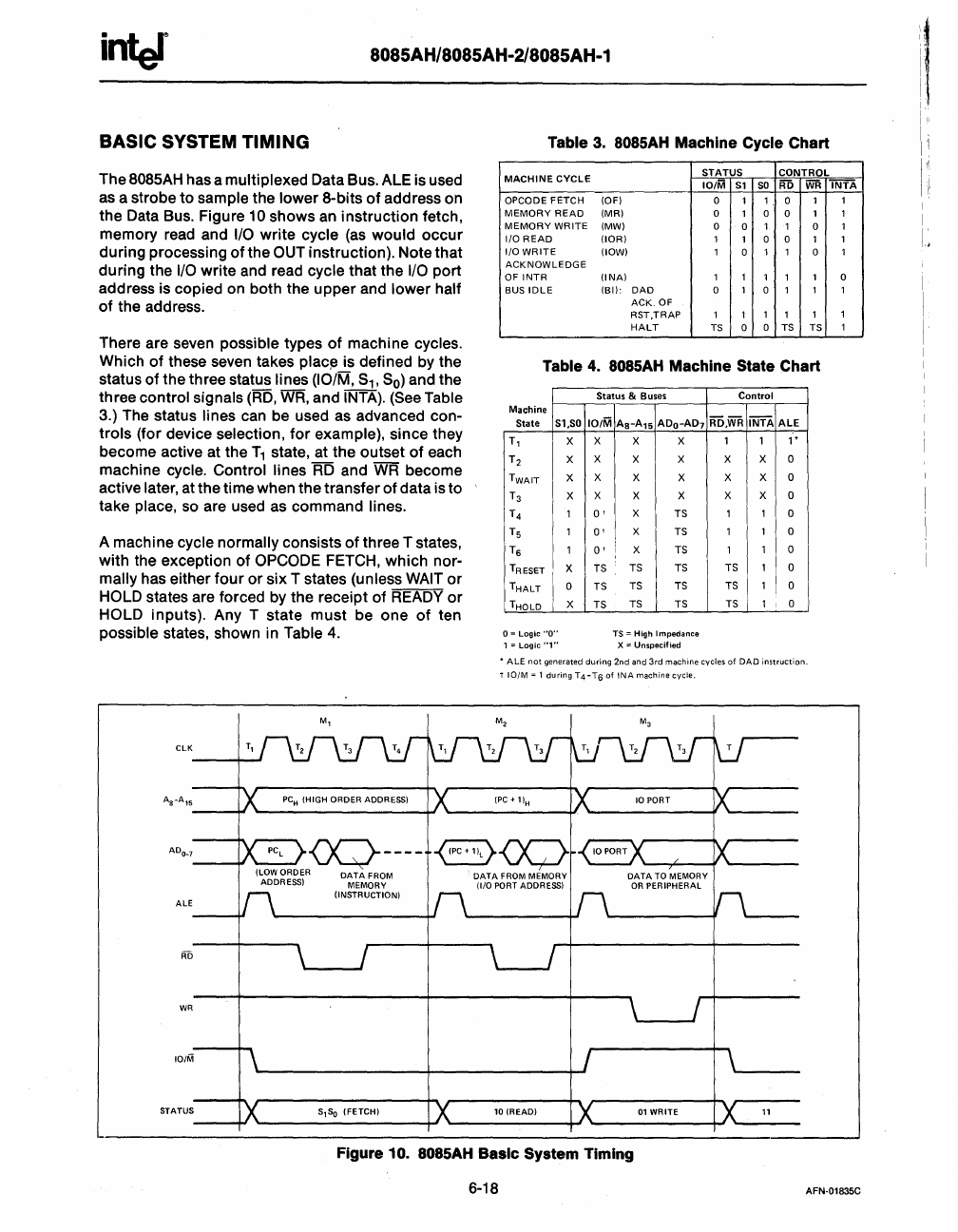

BASIC SYSTEM TIMING

The 8085AH has a multiplexed Data Bus. ALE is used

as

a strobe to sample the lower 8-bits

of

address on

the Data Bus. Figure

10

shows

an

instruction fetch,

memory read and

I/O

write cycle

(as

would occur

during processing

of

the OUT instruction). Note that

during the

I/O

write and read cycle that the

I/O

port

address is copied on both the upper and lower half

of

the address.

There are seven possible types

of

machine cycles.

Which

of

these seven takes

plac~

is defined by the

status

of

the three status lines (IO/M,

S1,

So)

and the

three control signals

(RD,

WR,

and

INTA).

(See Table

3.) The status lines can be used

as

advanced con-

trols (for device selection,

for

example), since they

become active at the

T1

state, at the outset

of

each

machine cycle. Control lines

RD

and

WR

become

active later, at the time when the transfer

of

data is to

take place,

so

are used as command lines.

A machine cycle normally consists

of

three T states,

with the exception

of

OPCODE FETCH, which nor-

mally has either

four

or six T states (unless

WAIT

or

HOLD states are forced by the receipt of READY

or

HOLD inputs). Any T state must be one

of

ten

possible states, shown in

Table 4.

ClK

T,

PC

H

(HIGH

ORDER

ADDRESS)

PC

l

~----

(LOW

ORDER

DATA

FROM

ADDRESS)

MEMORY

(INSTRUCTION)

ALE

WR

S,So

(FETCH)

Table 3. 8085AH Machine Cycle Chart

STATUS

CONTROL

MACHINE

CYCLE

101M

S1

so

RD

WR

OPCODE

FETCH

(OF)

0 1 1 0 1

MEMORY

READ

(MR)

0

1 0 0

1

MEMORY

WRITE

(MW)

0

0

1 1

0

1/0

READ

(lOR)

1

1

0 0 1

I/OWRITE

(lOW)

1

0

1 1 0

ACKNOWLEDGE

OFINTR

(INA)

1 1

1 1

1

BUS

IDLE

(BI):

DAD

0 1 0 1 1

ACK.OF

RST,TRAP

1 1

1

1

1

HALT

TS

0

0 TS TS

Table

4.

8085AH Machine State Chart

Machine

State

S1.S0

T,

T2

TWAIT

T3

T4

T5

Ts

T

RESET

I

THALT I

THOLD

0=

logic

"0"

, =

logic

"'"

X

X

X

X

1

1

1

X

0

X

Status & Buses

101M

As-A15

ADo-AD7

X X X

X

X X

X

X X

X X X

0'

X

TS

0'

X

TS

o t

I

X

TS

I

TS

TS

TS

TS

TS

TS

TS

TS TS

TS

= High

Impedance

x =

Unspecified

Control

Ro,WR

INTA

ALE

1 1

1"

X

X

0

X

X

0

X

X

0

1 1 0

1

1

0

1

1

0

TS

1

I

0

TS

1 0

TS 1

0

*

ALE

not

generated

during

2nd

and

3rd

machine cycles

of

DAD

instruction.

t 101M = ,

during

T4-T6

of

INA machine cycle.

10

(READ)

01

WRITE

l'

Figure 10. 8085AH Basic System Timing

INTA

1

1

1

1

1

0

1

1

1

6-18

AFN·01835C

II',

I.'

I

I"

I'!I

I,

I'I

I)

I

I

I'

I·,