FUNCTIONAL DESCRIPTION

M1

(OF)

SIGNAL

T1

T2

TWAIT

T3

T4

TS

TS

-

LI

LI LI

LI

L.I

L..I

LJ

ClK

101M,

I--

tx

IO/M-0,S1-1,SO-1

S1,SO

I--

I--

tx

AS-A16

PCH

UNSPECIFIED

I--

I--

OUT

IN

AD

O

·AD

7

tx

PCl

~<

DO.[)7 (DCX)

);-

-----

~---

-

~---

I--

!

j

ALE

v---\

J

I--

1

iffi

'~

......

READY

"'C..---

~

,....

"C---

~

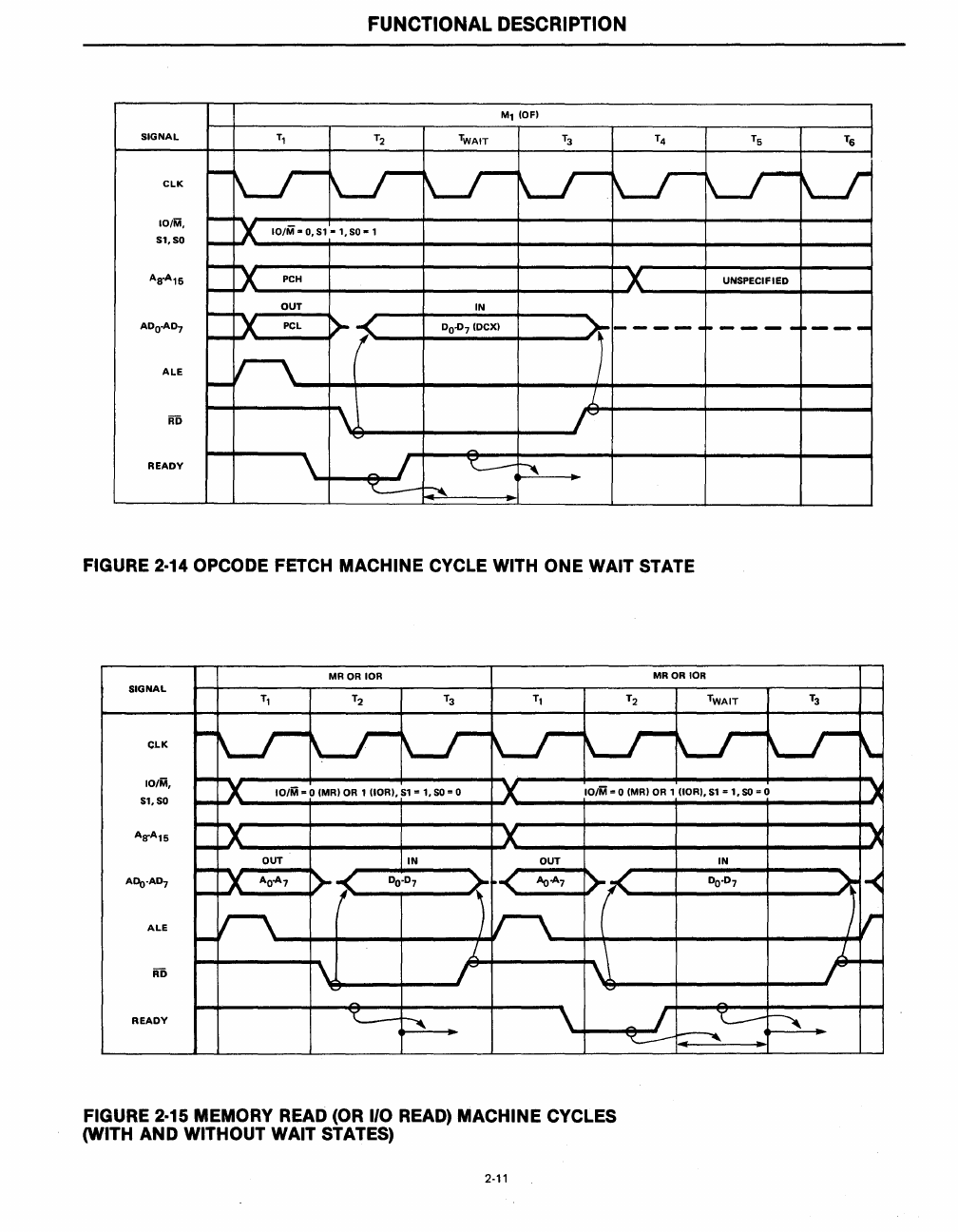

FIGURE 2·14 OPCODE FETCH MACHINE CYCLE WITH ONE WAIT STATE

MR OR lOR

MR OR lOR

SIGNAL

T1

T2 T3

T1

T2

TWA

IT

T3

....

'---.I'

~

LI

'---.I'

'---'

~

U-

~

C~K

-

101M,

101M = 0 (MR) OR 1 (lOR),

S1

= 1,

SO

= 0

101M = 0 (MR)

OR

1 (lOR),

S1

= 1,SO = 0

S1,SO

-

-

:x

AS"A1S

-

OUT

IN

OUT

-

)(

r>--{

>-

1>(

AOo·AD

7

AO-A7

D

O

·D

7

Ao-A7

....

!

)

ALE

1\

1\

~

1..

~

iffi

I~

....,

READY

'L--

N

FIGURE 2·15 MEMORY READ (OR

1/0

READ) MACHINE CYCLES

(WITH AND WITHOUT WAIT STATES)

2·11

""""

""C---

IN

D

O

·D

7

'C---

~

~

~

)(

)(

7

1-<

V-

f-

~