8085AH/8085AH-2/8085AH-1

As

in the 8080, the READY line is used

to

extend the

read and write

pulse lengths so that the 8085AH can

be used with

slow memory. HOLD causes the

CPU

to

relinquish the bus when it is through with

it

by float-

ing the Address and Data Buses.

SYSTEM

INTERFACE

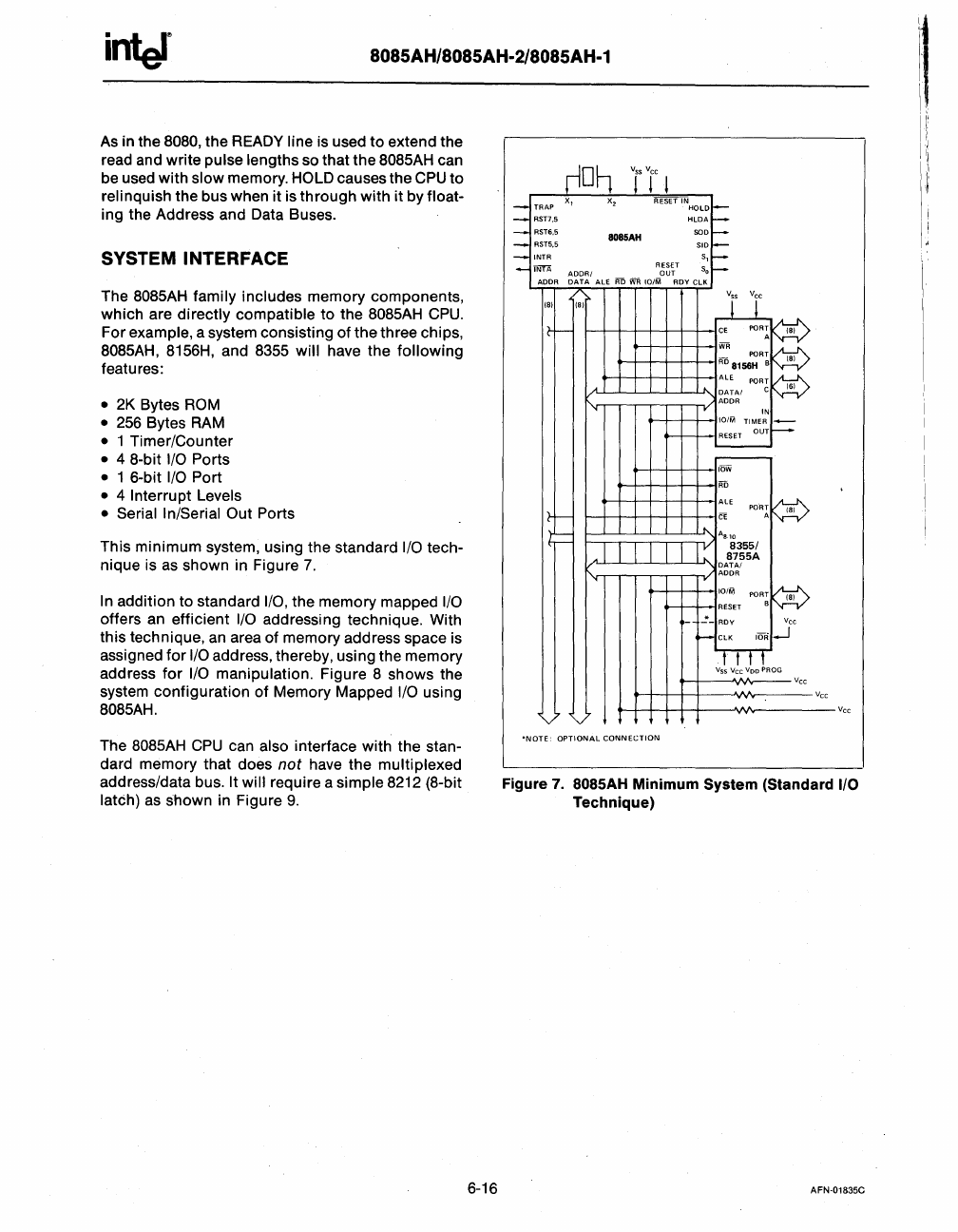

The 8085AH family includes memory components,

which are directly compatible to the 8085AH

CPU.

For example, a system consisting

of

the three chips,

8085AH, 8156H, and 8355 will have the following

features:

• 2K Bytes

ROM

• 256 Bytes

RAM

• 1 Timer/Counter

• 4 8-bit I/O Ports

• 1 6-bit

I/O

Port

• 4 Interrupt Levels

• Serial In/Serial Out

Ports

This minimum system, using the standard

I/O tech-

nique is as shown in Figure

7.

In

addition to standard

I/O,

the memory mapped

I/O

offers an efficient

I/O

addressing technique. With

this technique, an area of memory address space is

assigned

for

I/O address, thereby, using the memory

address

for

I/O

manipulation. Figure 8 shows the

system configuration of Memory Mapped I/O using

8085AH.

The 8085AH

CPU

can also interface with the stan-

dard memory that does

not have the multiplexed

address/data bus. It will require a simple 8212 (8-bit

latch) as shown in Figure

9.

6-16

riD~

vrvr

1

-

TRAP

X,

X

2

RESET IN

HOLD

I-

-

RST7.5

HLDA

f-

-

RST6.5

8085AH

SOD

f--

-

RST5.5

SIOI-

-

INTR

s,f-

-

jjij'fA

ADDRI

RESET

So

f--

OUT

ADDR

DATA

ALE AD

ii'iR

101M

ROY

eLK

181

18/

VI'

Vr

h-

~

POR:W

WR

~

_

PORT

181

RD

8156H 8

...

ALE

PORT~

DATAl

C

161

ADDR

"

IN

101M

TIMER

-

~)--

I-

RESET

OUT

I----

lOW

AD

ALE

~

PORT

Ih-

CE

A

'--

~A8.10

r-

h

8355/

8755A

DATAl

ADDR

~

~

101M

PORT

_l-

f-

RESET

8

-

--

ROY

Vee

~

CLK

IOR-1

t

tt

1

Vss Vee

Voo

PROG

Vee

Vee

~v

Vee

'NOTE:

OPTIONAL

CONNECTION

Figure

7.

8085AH Minimum System (Standard I/O

Technique)

AFN-01835C