TH~INSTRUCTION

SET

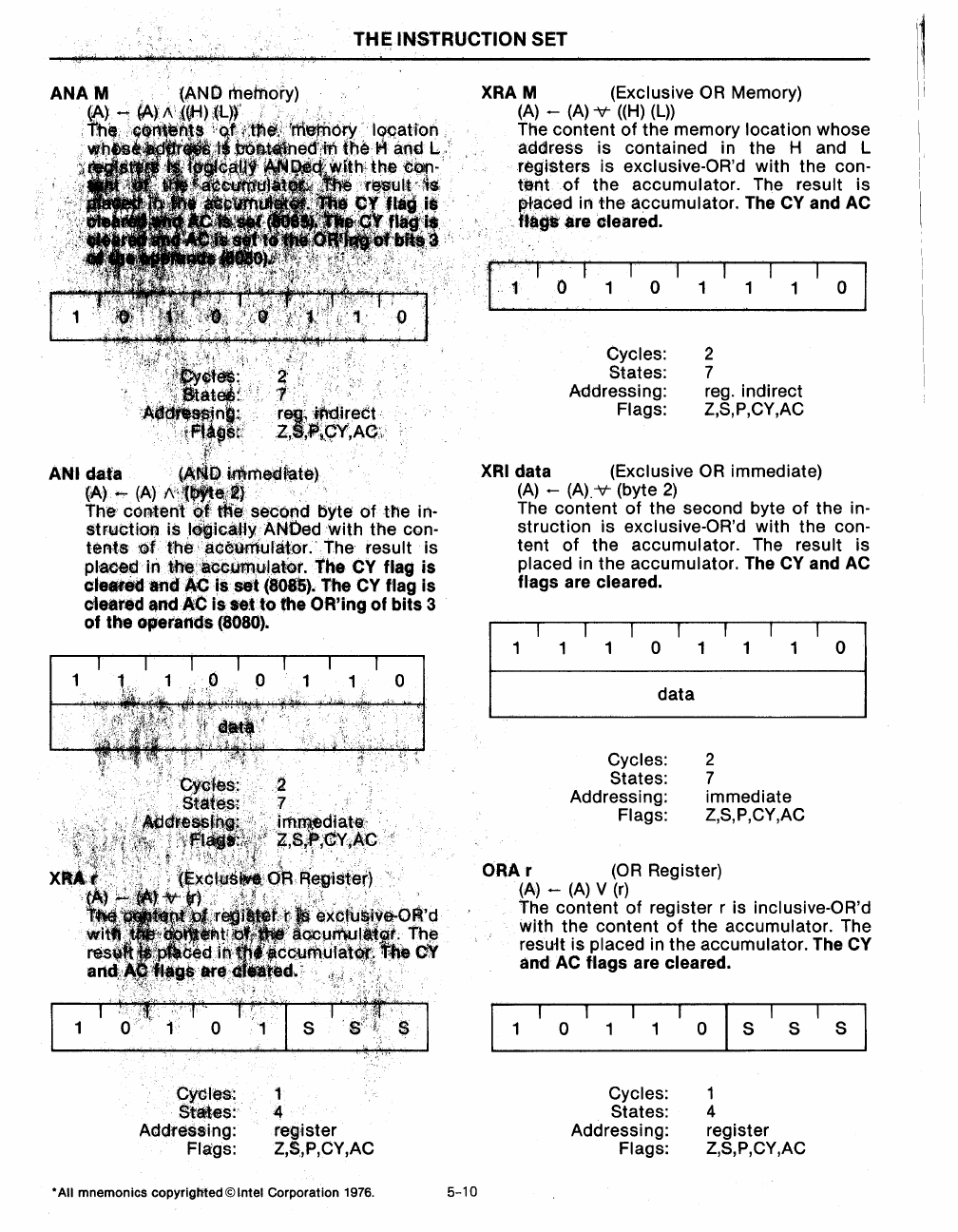

ANI

da.fa

1

(A)

....

(A)' N;"fllM8;rll

The~

cc>mteht

"

.....

secQnd

byte

of'

the

hi-

str4Jction is .

c.a~1y·

ANOed

with

the con-

te~ts

o:f·~he

'ace3mufator.'The

result is

pl~aee~

in'tr~;:acci.tm,u'atGt.

the

CV flag is

c:le

••

andAc,s .Ht(8oati}.

The

CV

f'lag is

cleared

andAC

is.elto

the OR'ing of bits 3

of

the operaftds

(8080).

Q-yGI$S:

Staltes:'

Add:ress,jng:

Flags:

1

4

register

Z,S,P,CY,AC

• All mnemonics copyrighted © Intel Corporation

1976,

5-10

XRA M (Exclusive

OR

Memory)

(A)

-

(A)

-v-

«H)

(L))

The content

of

the memory location whose

address is contained in the

Hand

L

registers is exclusive-OR'd with the con-

teotof

the accumulator. The result is

P'taced

in

the

accumulator. The

CY

and AC

. '

.......

e cleared.

1

o

1

o

Cycles:

States:

Addressing:

Flags:

1

2

7

1

1

reg. indirect

Z,S,P,CY,AC

o

XRI data (Exclusive

OR

immediate)

(A)

-

(A).-v-

(byte

2)

The content

of

the second byte

of

the in-

struction is exclusive-OR'd with the con-

tent

of

the accumulator. The result is

placed in the accumulator. The

CY

and AC

flags

are cleared.

1

1

1

o

data

Cycles:

States:

Addressing:

Flags:

1 1

2

7

immediate

Z,S,P,CY,AC

o

ORA r

(OR

Register)

1

(A) - (A) V (r)

The content of register r is inclusive-OR'd

w.ith

the content

of

the accumulator. The

resuH is placed in the accumulator. The CY

and

AC

flags are cleared.

o 1

1

o

Cycles:

States:

Addressing:

Flags:

S

S

1

4

register

Z,S,P,CY,AC

S

11

Ii

I