FUNCTIONAL DESCRIPTION

2.3.1

Multiplexed Bus Cycle Timing

The execution

of

any 8085A program consists

of a sequence

of

READ

and WRITE operations,

of which each transfers a byte

of

data between

the

8085A and a particular memory or

1/0

ad-

dress. These

READ

and WRITE operations are

the

only communication between the processor

and the other components, and are

all that is

necessary

to

execute any instruction or pro-

gram.

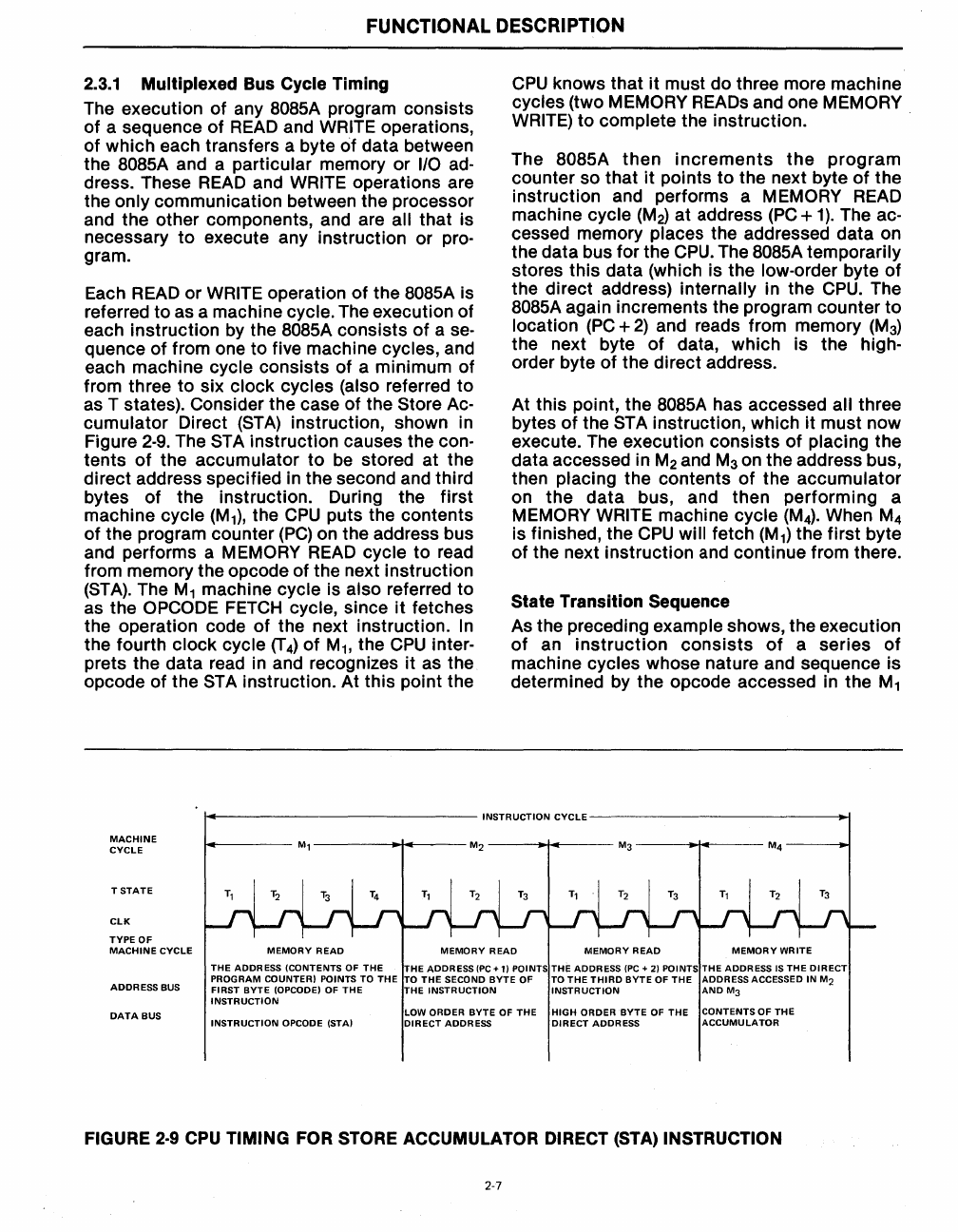

Each

READ

or WRITE operation

of

the 8085A is

referred

to

as a machine cycle. The execution of

each instruction by the

8085A consists

of

a

se-

quence

of

from one to five machine cycles, and

each machine

cycle consists

of

a minimum of

from three

to

six clock cycles (also referred

to

as T states). Consider the case

of

the Store Ac-

cumulator

Direct

(STA)

instruction, shown in

Figure

2-9. The STA instruction causes the con-

tents

of

the accumulator

to

be

stored at the

direct address specified in the second and third

bytes

of

the instruction. During the

first

machine cycle

(M

1

),

the

CPU

puts the contents

of

the program counter

(PC)

on the address bus

and performs a

MEMORY

READ

cycle to read

from memory the opcode

of

the next instruction

(STA).

The

M1

machine cycle is also referred

to

as the OPCODE

FETCH

cycle, since

it

fetches

the operation code

of

the next instruction.

In

the fourth clock cycle (T

4)

of

M

1

, the

CPU

inter-

prets the data read in and recognizes

it

as the

opcode of the

STA instruction. At this point the

CPU

knows that

it

must do three more machine

cycles (two MEMORY READs and one MEMORY

WRITE)

to complete the instruction.

The

8085A

then

increments

the

program

counter so that

it

points

to

the next byte

of

the

instruction and performs a

MEMORY READ

machine

cycle

(M

2

) at address

(PC

+ 1). The ac-

cessed memory places the addressed data on

the data bus for the

CPU.

The 8085A temporarily

stores this data (which is the low-order byte

of

the direct address) internally in the

CPU.

The

8085A again increments the program counter

to

location

(PC

+ 2) and reads from memory

(M3)

the next byte

of

data, which is the high-

order byte

of

the direct address.

At this point, the

8085A has accessed all three

bytes

of

the STA instruction, which it must now

execute. The execution consists

of

placing the

data accessed in

M2

and

M3

on the address bus,

then

placing the contents

of

the accumulator

on the

data

bus, and then performing a

MEMORY WRITE machine cycle

(M4).

When

M4

is finished, the

CPU

will fetch

(M

1

) the

first

byte

of

the next instruction and continue from there.

State Transition Sequence

As the preceding example shows, the execution

of

an

instruction

consists

of

a series

of

machine cycles whose nature and sequence is

determined by the opcode accessed in the

M1

~------------

INSTRUCTION

CYClE--------------.I

MACHINE

CYCLE

T

STATE

ClK

TYPE

OF

MACHINE

CYCLE

ADDRESS

BUS

MEMORY

READ

MEMORY

READ

MEMORY

READ

MEMORY

WRITE

THE

ADDRESS

(CONTENTS

OF

THE

THE

ADDRESS

(PC+ 1) POINTS

THE

ADDRESS

(PC

+ 2) POINTS THE

ADDRESS

IS

THE

DIRECT

PROGRAM

COUNTER)

POINTS

TO

THE

TO

THE

SECOND

BYTE

OF

TO

THE

THIRD

BYTE

OF

THE

ADDRESS

ACCESSED

IN

M2

FIRST

BYTE

(OPCODE) OF

THE THE

INSTRUCTION INSTRUCTION

AND

M3

INSTRUCTION

DATA

BUS

lOW

ORDER

BYTE

OF

THE

HIGH

ORDER

BYTE

OF

THE

CONTENTS

OF

THE

INSTRUCTION

OPCODE (STA)

DIRECT

ADDRESS

DIRECT

ADDRESS

ACCUMULATOR

FIGURE

2·9

CPU

TIMING

FOR

STORE

ACCUMULATOR DIRECT

(STA)

INSTRUCTION

2-7