SYNC

DBIN

READY

WAIT

WR

STATUS

INFORMATION

Ml

Tl

T2

T3

T4

Tl

_rL-

"rL-

rL.-

h-

rL-

_-.-1\

~~

Wt

Wt.Jl

- -

--

----'

BYTE

\UNKNOWNJ

ONE

-

--

-

-'t----l

\.

11-

j

I

FLOATING

-~

\

J

1

1

\

"'"

"0"

"'"

18

NOTE: @ Refer

to

Status

Word

Chart

on Page

4-6.

M2

M3

T2

T3

Tl

T2 T3

h-

h-

rL-

rL-

r-L-

Jt

~

Jt

~I~

--

BYTE

X

INP~T

DATA

TO

TWO

ACCUMULATOR

\.

~J

----,

.

\.

_J

\ I \

I \ I

'-

X0

X0

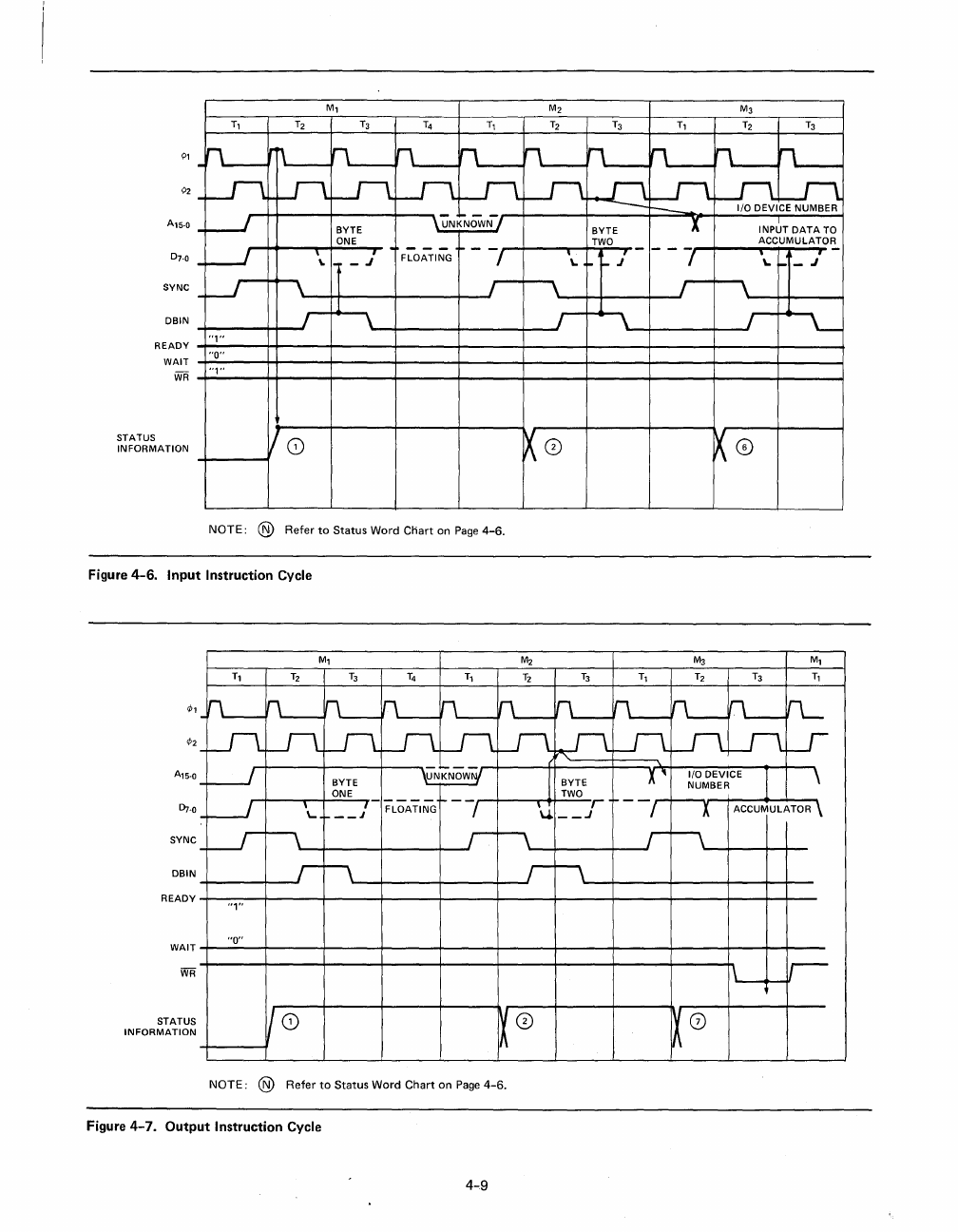

Figure

4-6.

Input Instruction Cycle

<1>,

0]'0

SYNC

DBIN

READY

WAIT

STATUS

INFORMATION

T,

_fL-

--.Il

_-.1

---'

---'

"'"

"0"

M,

T2

T3

fL-

rL-

--.Il

l-.J\.

BYTE

ONE

'L.

I

__

J

~

,-

1\

1/8

M2

T4

T,

T2

T3

rL-

rL-

rL-

fL-

Ul

u--1 u--1

Jl

--

UNKNOW

1 BYTE

----

'--

I

TWO

FLOATING

'u

r

__

J

r

~

,-

\

1~0

NOTE: @

Refer

to

Status

Word

Chart

on

Page

4-6.

Figure

4-7.

Output

Instruction Cycle

4-9

MJ

M,

T,

T2

T3

T,

rL-

fL-

rL-

V"L

Ul

L-Fl

Ul

U-

X'

110

DEVICE

\

NUMBER

--

X

ACCUMULATOR

r

1\

\

Ir-

-

~0