I

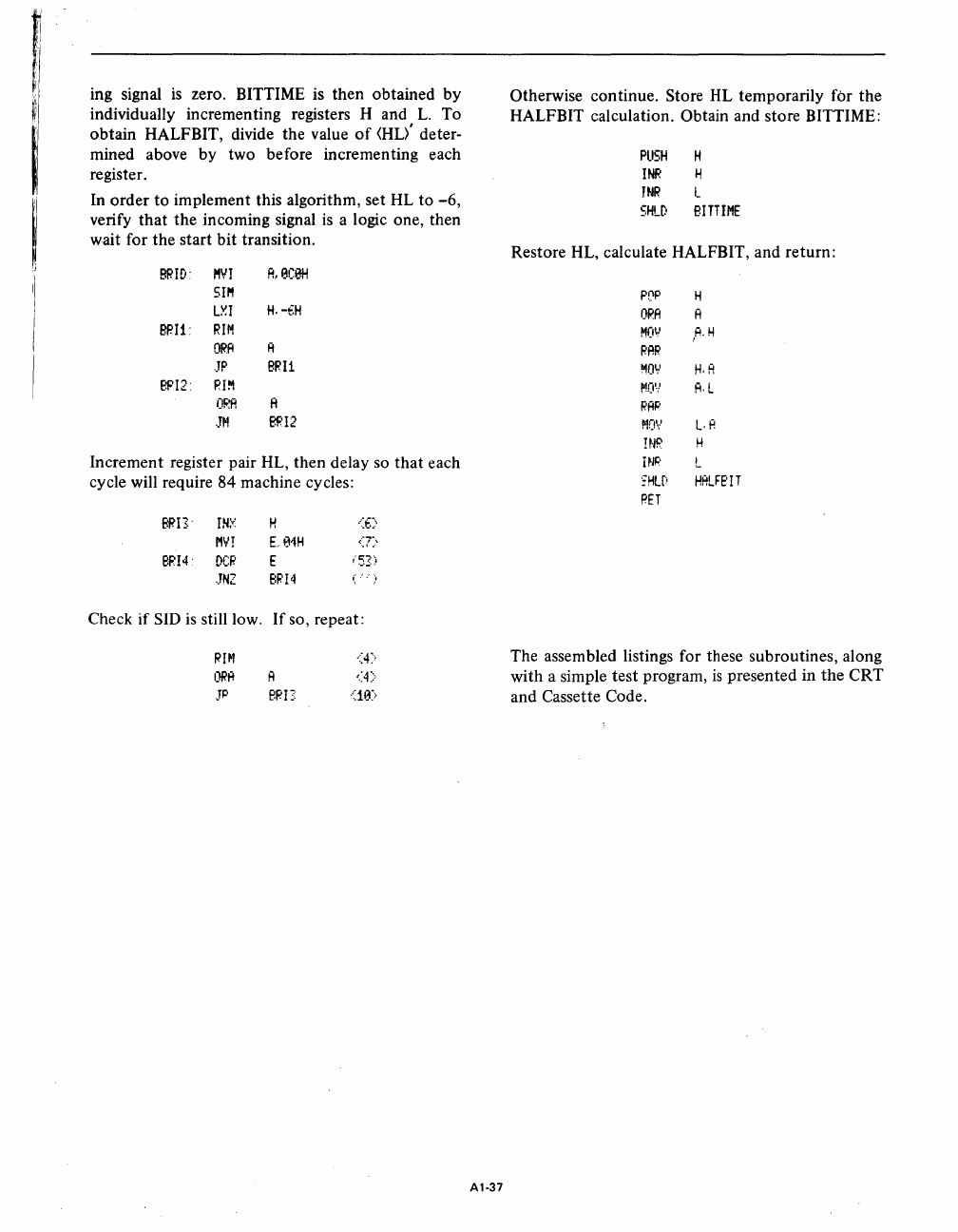

ing signal

is

zero. BITTIME is then obtained

by

individually incrementing registers

Hand

L.

To

obtain HALFBIT, divide the value

of

(HU'

deter-

mined above by two before incrementing each

register.

In order

to

implement this algorithm, set HL

to

-6,

verify that the incoming signal

is

a logic one, then

wait for the start bit transition.

BP.ID:

MVI

A,

eCeH

SIP'!

LXI

H.-€H

BP.I1:

RIM

ORft

A

..Ip

BRI!

BF'I2:

RI!1

ORA

A

..IM

BPI2

Increment register pair HL, then delay so

that

each

cycle will require 84 machine cycles:

Bf?E'

II";':

H

<6>

MYI

E.

01H

(7)

BRl4

'

DCR

E

"51.)

..TNZ

BP.I4

I

}

Check

if

SID

is

still low.

If

so, repeat:

PHI

<4>

OPR

Ii

<4}

JP

BPI::

<113)

A1-37

Otherwise continue. Store

HL

temporarily for the

HALFBIT calculation.

Obtain and store BITTIME:

PUSH

H

INP

H

TNR

L

SHLD

BITTIME

Restore HL, calculate HALFBIT, and return:

ppp

H

ORA

A

MOil

,A.H

RAP.

b10V

H.H

MO',,.'

A·l

PAf;'

~IO"'!

L·

A

WP

H

HIP

L

::HLf:o

HAlJE'

IT

PET

The assembled listings for these subroutines, along

with a simple test program,

is

presented in

the

CRT

and Cassette Code.