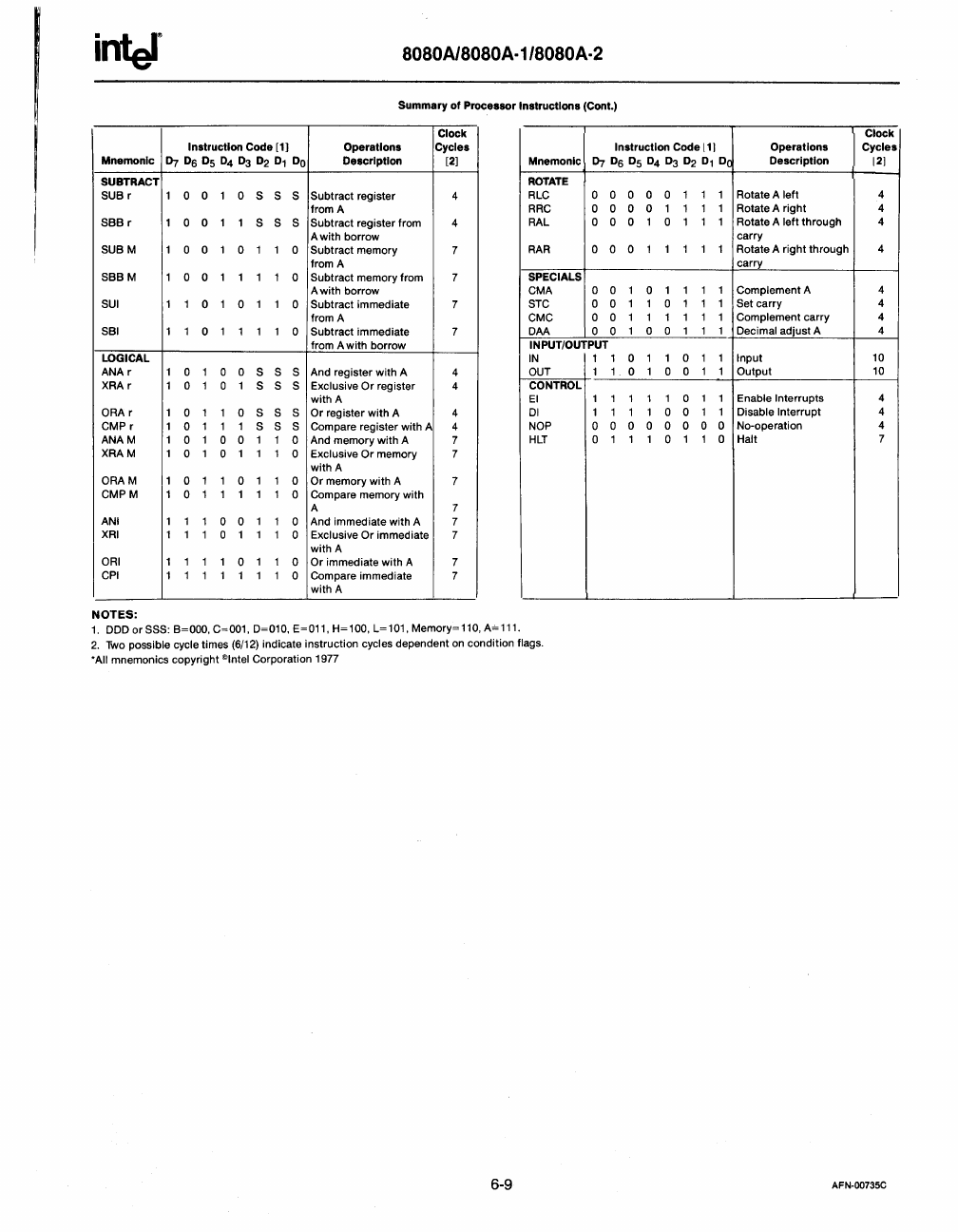

inter

8080A/8080A·1/8080A·2

Summary

of

Processor Instructions (Cont.)

Clock

Instruction

Code [1)

Operations Cycles

Instruction Code

11

J

Mnemonic

D]

D6

Ds

D4 D3

D2

D1

Do

Description

[2)

Mnemonic

D]

D6

Ds

D4 D3 D2

D1

Do

SUBTRACT

ROTATE

SUBr

1

0

0

1 0

S S S Subtract

register 4

RLC

0

from A

RRC

0

SBB

r 1

0 0

1 1

S S S Subtract register from 4

RAL 0

A with borrow

SUBM

1

0 0

1

0 1 1 0 Subtract memory

7

RAR

0

from A

SBBM

1

0 0

1 1 1

1

0 Subtract memory from 7

SPECIALS

A with borrow CMA

0

SUI

1 1

0

1

0

1 1

0 Subtract immediate 7

STC

0

from A

CMC 0

SBI

1 1

0

1

1 1 1

0 Subtract immediate 7

OM

0

from A with borrow

INPUT/OUTPUT

LOGICAL

IN

ANA r 1 0 1

0

0

S S S

And register with A

4

OUT

XRA r 1 0 1

0

1

S S S Exclusive

Or

register 4

CONTROL

with A

EI

ORAr

1

0

1

1

0 S S S

Or

register with A 4

01

CMPr

1

0

1

1

1

S S S Compare register with A 4

NOP

ANAM

1

0

1

0 0

1

1

0 And memory with A 7

HLT

XRAM

1

0

1

0

1 1 1

0 Exclusive

Or

memory 7

with A

ORAM

1

0

1 1

0

1

1

0

Or

memory with A

7

CMPM

1

0

1 1 1 1 1

0 Compare memory with

A 7

ANI 1 1 1

0 0

1 1

0

And immediate with A

7

XRI

1 1 1

0

1 1 1

0 Exclusive

Or

immediate 7

with A

ORI

1 1 1 1

0

1 1

0

Or

immediate with A 7

CPI

1 1 1 1 1 1 1

0 Compare immediate 7

with A

NOTES:

1.

DOD

orSSS:

B=OOO,

C=OOl, 0=010, E=011, H=100, L=101, Memory=110, A=111.

2.

Two

possible cycle times

(6/12)

indicate instruction cycles dependent on condition flags.

'AII mnemonics copyright

©Intel

Corporation 1977

6-9

1

1

1

1

0

0

0 0 0 0

1

1 1

0 0 0

1 1 1 1

0 0

1

0 1 1

1

0 0 1

1 1 1 1

0 1 0 1 1 1

1

0

1 1

0

1 1 1

0

1 1 1 1 1 1

0

1 0

0

1 1

1

1

0

1 1 0 1 1

1

0

1

0 0

1 1

1 1 1 1

0

1 1

1 1 1

0 0

1 1

0

0 0 0 0 0 0

1

1 1

0

1 1 0

Clock

Operations

Cycles

Description

12J

Rotate A left 4

Rotate A right 4

Rotate A left through 4

carry

Rotate A right through

4

carry

Complement A

4

Set carry 4

Complement carry 4

Decimal adjust A

4

Input

10

Output

10

Enable Interrupts

4

Disable

Interrupt

4

No-operation

4

Halt

7

AFN·OO735C