I

,

A1

5

A8

11

STB

D08--DOl

13

ALE

r----

DS2

-f

MD

8212

CUi

~

DI8

--

Dll

DSl

AD7

'-

I

I

ADO

74LS36~

B08SA

7~

RD

J I

MEMR

~~

lOR

WR

-

~

MEMW

I

1>-=11

~~

D-~

lOW

101M

74LS04

74LS04Lt

~

HOLD

HLDA

CLK(OUn

RESET

IN

r------

RESET

RESET OUT

f---

'-

~

-

74LS04~

-

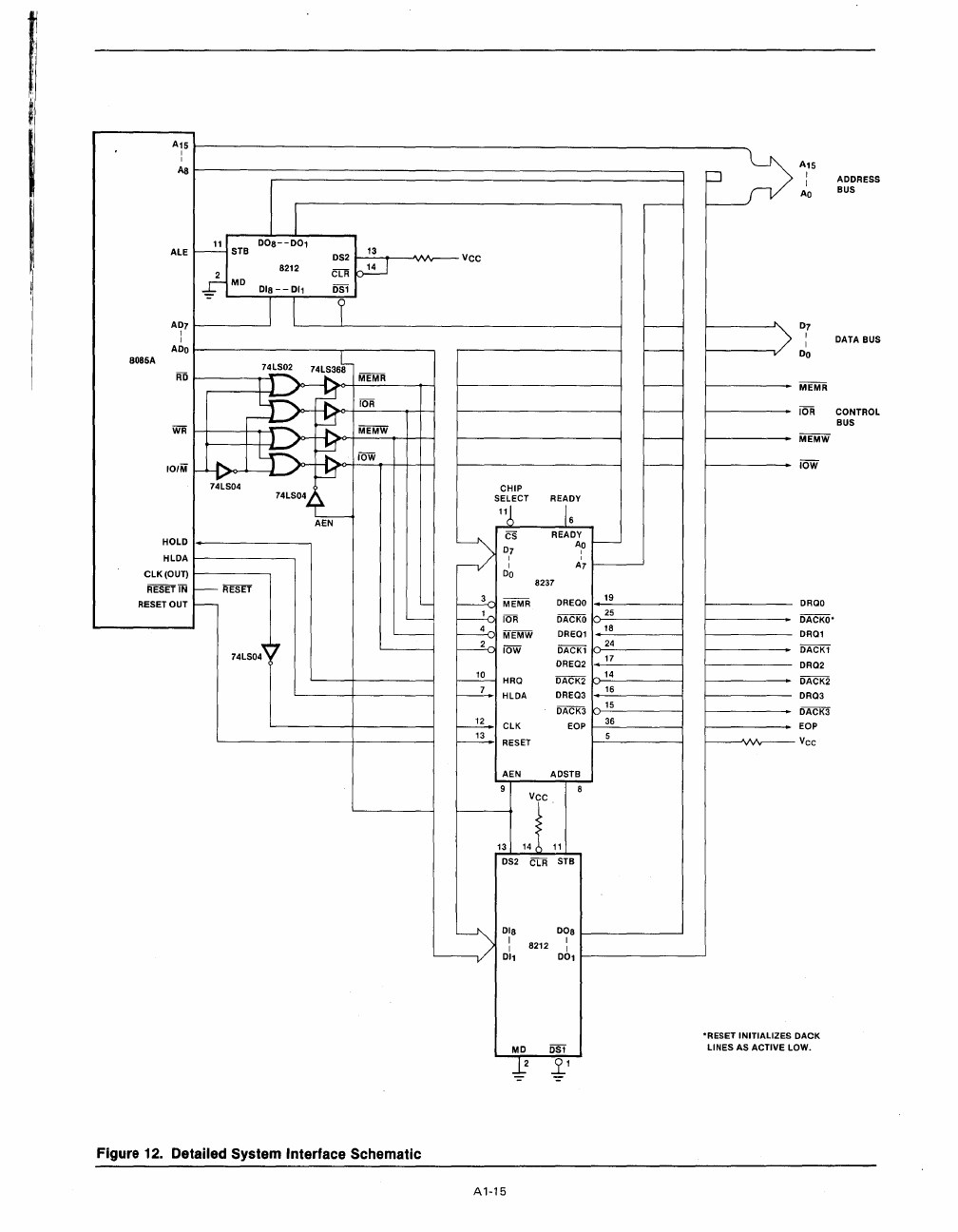

Figure 12. Detailed System Interface Schematic

VCC

CHIP

SELECT

READY

116

16

=>

CS

READY

A,O

D,7

A

'

7

I

DO

8237

~

MEMR

DREao

~

iOR

DACKO

~

MEMW

DREOl

t----2o

lOW

DACKl

DRE02

~

HRa

DACK2

r-----2-

HLDA

DREa3

DACK3

r---E--

CLK

EOP

~

RESET

AEN ADSTB

9

8

13

I

14

11

DS2

CLR

STB

~

DI8

D08

I

8212

I

I I

Dll

DOl

MD

DSl

J.2

.1.

1

A1-15

.---

~

r----

"

f---

r----

r----

r---

r--

'----

I---

19

25

18

24

17

14

16

15

36

5

·RESET INITIALIZES

LINES AS ACTIVE

L

A15

I

I

AO

D7

I

I

Do

MEMR

lOR

MEMW

lOW

DRao

DACKO·

DROl

DACKl

DR02

DACK2

DR03

DACK3

EOP

Vee

DACK

OW.

ADDRESS

BUS

DATA BUS

CONTROL

BUS