8080Al8080A·1/8080A·2

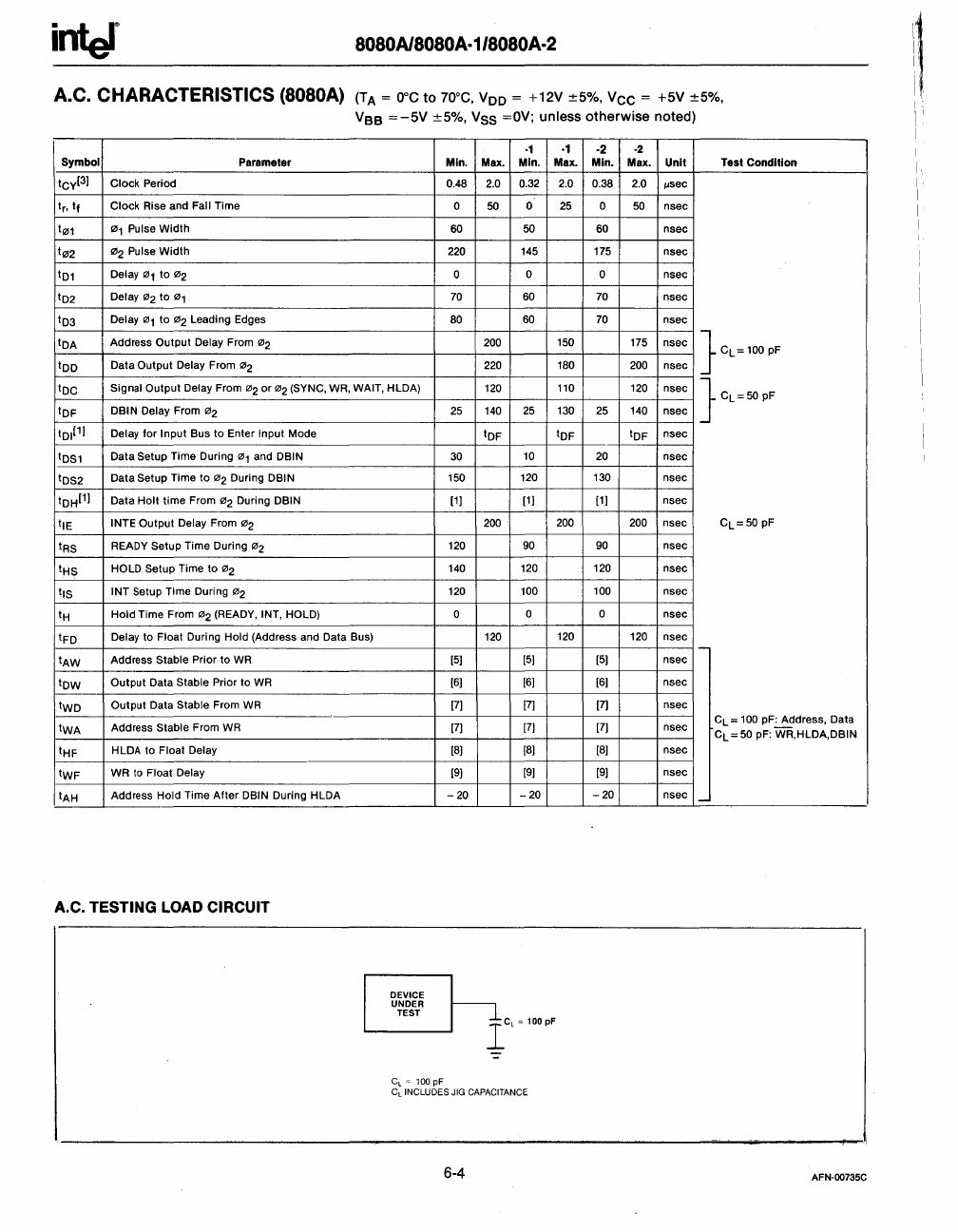

A.C. CHARACTERISTICS (8080A)

(TA

=

O°C

to

70°C,

VOO

= +12V ±5%,

Vee

=

+5V

±5%,

Vee

=

-5V

±5%,

Vss

=OV; unless otherwise noted)

·1

·1

·2

·2

Symbol Parameter

Min. Max.

Min.

Max. Min. Max.

Unit

Test Condition

tCy(3)

Clock Period

0.48 2.0

0.32 2.0 0.38

2.0

"sec

tr,tl

Clock Rise and Fall Time

0

50

0

25

0

50

nsec

t01

01

Pulse

Width

60

50

60

nsec

t02

02

Pulse

Width

220

145 175 nsec

tD1

Delay

01

to

02

0

0

0

nsec

tD2

Delay 02

to

01

70

60

70

nsec

tD3

Delay

01

to

02

Leading Edges

80

60

70

nsec

tDA

Address

Output Delay From 02

200

150 175 nsec

}CL=100

pF

too

Data Output Delay From

02

220

180

200

nsec

tDC

Signal Output Delay From 02 or 02 (SYNC, WR, WAIT, HLDA)

120

110 120 nsec

}

CL=50pF

tDF

DBI N Delay From 02

25

140

25

130

25

140 nsec

tOl[11

Delay for Input Bus

to

Enter Input Mode

tDF tDF tDF

nsec

tDS1

Data Setup Time During

01

and DBIN

30

10

20

nsec

tDS2

Data Setup Time to

02

During DBIN 150

120

130 nsec

tDH(1)

Data

Holt

time

From 02 During DBIN

(1)

(1)

(1)

nsec

tiE

INTE Output Delay From 02

200

200

200

nsec

CL=50

pF

tRS

READY Setup Time During 02

120

90 90

nsec

tHS

HOLD Setup

Time to 02

140

120 120 nsec

tiS

INT Setup Time During 02

120

100

100

nsec

tH

Hold Time From 02 (READY, INT, HOLD) 0

0 0

nsec

tFO

Delay to Float During Hold (Address and Data Bus)

120

120 120

nsec

-

tAW

Address Stable Prior

to

WR

(5)

(5)

(5)

nsec

tow

Output Data Stable Prior to

WR

(6)

(6)

(6)

nsec

two

Output Data Stable From

WR

(7)

(7)

(7)

nsec

tWA

Address Stable From

WR

(7)

(7) (7)

nsec

CL =

100 pF: Address, Data

CL =

50

pF: WR,HLDA,DBIN

tHF

HLDA to

Float Delay

(8)

(8)

(8)

nsec

tWF

WR

to

Float Delay

(9)

(9) (9)

nsec

tAH

Address

Hold Time After DBIN During HLDA

-20

-20

-

20

nsec

-

A.C. TESTING LOAD CIRCUIT

DEVICE

UNDER

lC'~"'"

TEST

Cl~

100pF

C

l

INCLUDES JIG CAPACITANCE

--

6-4

AFN-00735C