FUNCTIONAL DESCRIPTION

instruction, which enables

or

disables

thes.e

in-

terrupts by clearing or setting corresponding

mask flags based on data in the accumulator.

(See

Figure

2-4.)

You may read the status

of

the

interrupt mask previously set by peforming a

RIM

instruction. Its execution loads into the ac-

cumulator

the

following

information.

(See

Figure

2-5.)

• Current interrupt mask status for the

RST

5.5,6.5, and 7.5 hardware status.

• Current interrupt enable flag status

(ex-

cept that immediately following

TRAP,

the I E flag status preceding that inter-

rupt is loaded).

•

RST

5.5,6.5, and

7.5

interrupts pending.

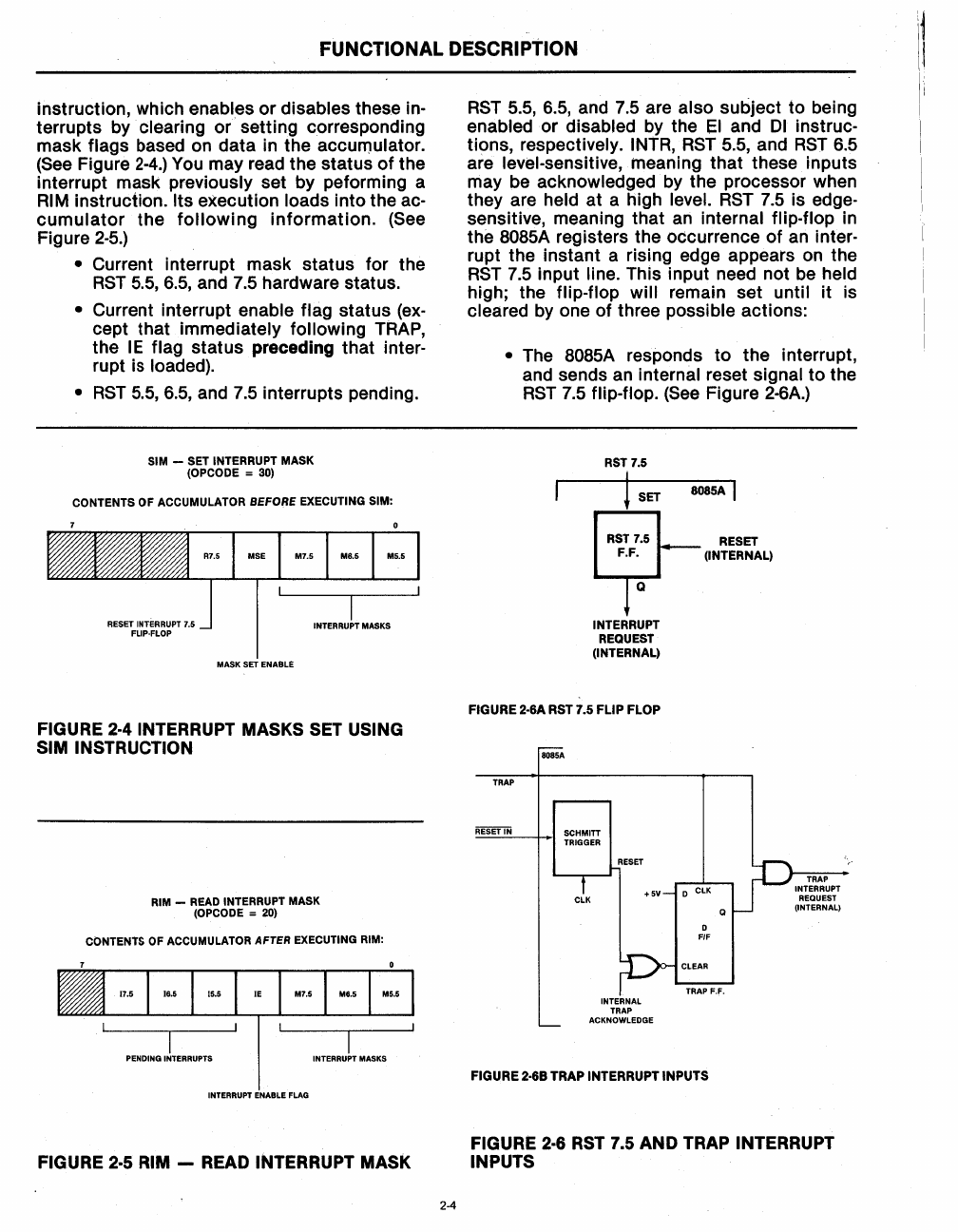

SIM - SET INTERRUPT

MASK

(OPCODE =

30)

CONTENTS OF ACCUMULATOR

BEFORE

EXECUTING SIM:

RESET INTERRUPT 7.5

FLlp·FlOP

MASK

SET

ENABLE

I

INTERRUPT

MASKS

FIGURE 2·4 INTERRUPT MASKS SET USING

SIM INSTRUCTION

RIM - READ INTERRUPT MASK

(OPCODE = 20)

CONTENTS OF ACCUMULATOR

AFTER EXECUTING RIM:

I I

PENDING INTERRUPTS

INTERRUPT MASKS

INTERRUPT

ENABLE FLAG

FIGURE 2·5 RIM - READ INTERRUPT MASK

2-4

RST

5.5,

6.5,

and

7.5

are also subject to being

enabled or disabled by the

EI

and

01

instruc-

tions, respectively. INTR,

RST

5.5,

and

RST

6.5

are level-sensitive, meaning

that

these inputs

may be acknowledged by the processor when

they are held at a high

level.

RST

7.5

is edge-

sensitive, meaning that

an

internal flip-flop in

the

BOB5A

registers the occurrence

of

an

inter-

rupt the instant a rising edge appears on the

RST

7.5

input line. This input need not be held

high; the flip-flop

will remain set until

it

is

cleared by one

of

three possible actions:

• The

BOB5A

responds

to

the interrupt,

and sends an internal reset signal

to

the

RST

7.5 flip-flop.

(See

Figure

2-6A.)

RST 7.5

! SET 808SA I

I

Ry~51'

(IN~~~A~

INTERRUPT

REQUEST

(INTERNAL)

FIGURE 2·6A RST

7.5

FLIP FLOP

8085A

TRAP

REsET1iii

SCHMIIT

TRIGGER

RESET

ClK

+5V D

ClK

o

F/F

CLEAR

Q

TRAP

F.F.

INTERNAL

TRAP

ACKNOWLEDGE

FIGURE

2·68

TRAP INTERRUPT INPUTS

TRAP

INTERRUPT

REQUEST

(INTERNAL)

FIGURE 2·6 RST

7.5

AND TRAP INTERRUPT

INPUTS

I

ii,'.

I

Ii

I

I

I

I

I

I