MCS·S5™

SPECIAL PERIPHERAL

COMPONENTS

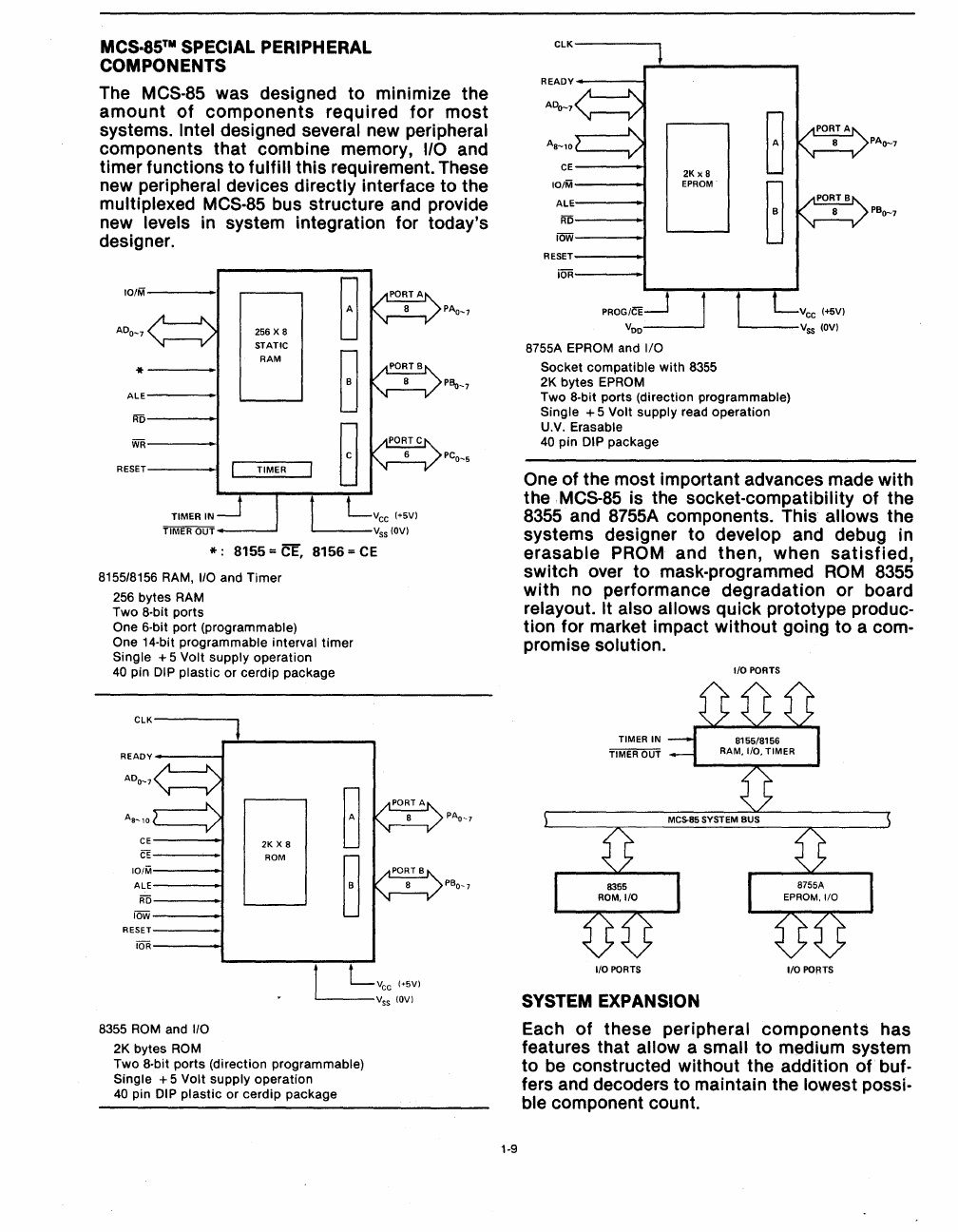

The MCS-85 was designed

to

minimize the

amount

of

components

required

for

most

systems. Intel designed several new peripheral

components

that

combine memory,

110

and

timer functions

to

fulfill

this requirement. These

new peripheral devices directly interface

to

the

multiplexed

MCS-85

bus structure and provide

new levels in system integration for today's

designer.

101;;;----1

*---

..

,

AlE----1

AD---

....

ViiR---

..

'

RESET---",

TIMER IN

256 X 8

STATIC

RAM

TIMER

TIMER

OUT-------'

~Vee(+5V)

Vss

(OV)

*:

8155 =

CE,

8156 =

CE

8155/8156

RAM,

1/0

and Timer

256 bytes

RAM

Two 8·bit ports

One 6·bit port (programmable)

One 14·bit programmable interval

timer

Single + 5 Volt supply operation

40

pin DIP

plastic

or cerdip package

8355

ROM

and 1/0

2K bytes

ROM

~VCCI+5VI

vss IOVI

Two 8·bit

ports

(direction programmable)

Single + 5 Volt supply operation

40

pin DIP

plastic

or cerdip package

1·9

ClK

READY

ADo-7

A

s

-

lO

CE

101M

ALE

AD

iOW

RESET

lOR

2K x 8

EPROM

PROG/CE~

Voo

8755A EPROM and I/O

Socket compatible

with

8355

2K bytes EPROM

0

G

Vee (+5V)

L..---Vss

(OV)

Two 8·bit ports (direction programmable)

Single + 5 Volt supply read operation

U.V.

Erasable

40

pin DIP package

One

of

the most important advances made

with

the

MCS-85

is the socket-compatibility

of

the

8355 and 8755A components. This allows the

systems designer

to

develop and debug in

erasable

PROM and

then,

when

satisfied,

switch over

to

mask-programmed

ROM

8355

with

no performance

degradation

or

board

relayout. It also allows

quick

prototype produc-

tion for market impact

without

going

to

a com-

promise solution.

TIMER IN

TIMER OUT

1/0

PORTS

SYSTEM EXPANSION

1/0

PORTS

I/O

PORTS

Each

of

these peripheral

components

has

features that allow a small

to

medium system

to

be constructed without the addition

of

buf-

fers and decoders

to

maintain the lowest possi-

ble component count.